# ULTRA-LOW POWER WIRELESS SENSOR CIRCUITS FOR IOT APPLICATIONS

ZHONGXIA SHANG

### A DISSERTATION SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

GRADUATE PROGRAMME IN ELECTRICAL ENGINEERING AND COMPUTER SCIENCE YORK UNIVERSITY TORONTO, ONTARIO

AUGUST 2020

© ZHONGXIA SHANG, 2020

#### ABSTRACT

Wireless sensors, which are responsible for local data acquisition, processing and communication, play an important role in Internet of Things (IoT) applications. This research focuses on two basic components in wireless sensors, i.e., the low-power frequency tunable wireless receiver and the power management unit (PMU) for autonomous operation.

In IoT applications, different sensors may need to operate in different frequency bands in order to meet environment constraints and industrial/medical standards. Thus, it is highly desirable to design a frequency configurable wireless receiver that provides flexibility in operation frequency. A 4-path filter based frequency shift keying (FSK) receiver is proposed to meet such a need, where the carrier frequency can be adjusted without changing the circuit. In addition, the proposed receiver requires no low-noise amplifier (LNA), which boosts the power efficiency. Frequency synthesizer is critical in FSK transceiver as it provides an accurate reference frequency. Based on 4-path mixer, a novel two-step calibration frequency synthesizer structure is proposed for low power consumption and wide locking range. Measurement results show that the proposed receiver achieves an energy per bit as 74pJ/bit with 2.5Mbps data rate and 184 $\mu$ W power consumption. Post-layout simulation results show that the proposed frequency synthesizer has a figure of merit (FOM) value as 1.4 $\mu$ W/MHz with 220MHz tuning bandwidth and 305 $\mu$ W power consumption. Autonomous operation is another requirement for the sensors in many IoT applications, such as wearable sensors. Energy harvester is commonly used for autonomous sensors, where a PMU with low start-up voltage is necessary. To meet such a requirement, a novel controller for PMU is proposed to boost the power efficiency under very low load current. The proposed PMU can be started up with input voltage as low as several tens of millivolts. The novel controller costs little power and the overall efficiency is increased. Also, a hardware efficient maximum power point tracking (MPPT) algorithm which is suitable for energy source with fixed internal resistance is proposed. Measurement results show that the proposed system has a low controller power as 3.6µW and the overall conversion efficiency is 83.9%.

#### ACKNOWLEDGEMENTS

Firstly, I would like to express my deep gratitude and appreciation to my supervisor, Dr. Peter Lian, for his guidance, support and encouragement throughout my PhD study. He shared me with his insight and knowledge to solve scientific problems; he spent time helping me apply for scholarships and revise papers; and he also gave me advice on how to take care of newborn baby. I could not have imagined having a better supervisor for the unforgettable four years.

I would also like to thank the members of my supervisory committee, Dr. Ebrahim Ghafar-Zadeh and Dr. Sebastian Magierowski. Their feedback on my qualification report and dissertation proposal helped me find a clearer way to conduct this research.

I need to thank all my lab mates, Dr. Yang Zhao, who provided me great help in the design and testing of each chip, Dr. Chundong Wu, who gave me suggestions on the power management unit design, and Dr. Hao Wang, for his nice tips on paper drafting.

I need to thank Dr. Li Geng for her support on the PMU chip design and for her revision comments on the paper. I also need to thank Mr. Andrew Marshall, for his help throughout my industrial internship.

Finally, I would like to thank all my family members for their support. I want to express special thanks to my beloved wife, Furui Hou. Her companionship is fundamental to the success of my PhD study, let alone the cute baby boy she brought to us.

### LIST OF PUBLICATIONS

- [1]. Z. Shang, Y. Zhao, W. Gou, L. Geng and Y. Lian, "83.9% Efficiency 100-mV Self-Startup Boost Converter for Thermoelectric Energy Harvester in IoT Applications," in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2020.2999331.

- [2]. Z. Shang, Y. Zhao and Y. Lian, "A Low Power Frequency Tunable FSK Receiver Based on the N-Path Filter," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 10, pp. 1708-1712, Oct. 2019, doi: 10.1109/TCSII.2019.2931840.

- [3]. Y. Zhao, Z. Shang and Y. Lian, "A 13.34 μW Event-Driven Patient-Specific ANN Cardiac Arrhythmia Classifier for Wearable ECG Sensors," in *IEEE Transactions on Biomedical Circuits and Systems*, vol. 14, no. 2, pp. 186-197, April 2020, doi: 10.1109/TBCAS.2019.2954479.

- [4]. Y. Zhao, Z. Shang and Y. Lian, "A 2.55 NEF 76 dB CMRR DC-Coupled Fully Differential Difference Amplifier Based Analog Front End for Wearable Biomedical Sensors," in *IEEE Transactions on Biomedical Circuits and Systems*, vol. 13, no. 5, pp. 918-926, Oct. 2019, doi: 10.1109/TBCAS.2019.2924416.

- [5]. Y. Zhao, Z. Shang and Y. Lian, "Auto Generation of High-Performance Fixed-Point Multiplier for Artificial Neural Networks," 2019 IEEE International

*Conference on Artificial Intelligence Circuits and Systems (AICAS)*, Hsinchu, Taiwan, 2019, pp. 1-5, doi: 10.1109/AICAS.2019.8771573.

- [6]. Y. Zhao, S. Lin, Z. Shang and Y. Lian, "Classification of Cardiac Arrhythmias Based on Artificial Neural Networks and Continuous-in-Time Discrete-in-Amplitude Signal Flow," 2019 IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), Hsinchu, Taiwan, 2019, pp. 175-178, doi: 10.1109/AICAS.2019.8771620.

- [7]. Z. Shang, Y. Zhao and Y. Lian, "Low Power FIR Filter Bank for EEG Processing Using Frequency-Response Masking Technique," 2018 IEEE 23rd International Conference on Digital Signal Processing (DSP), Shanghai, China, 2018, pp. 1-5, doi: 10.1109/ICDSP.2018.8631551.

- [8]. Y. Zhao, Z. Shang and Y. Lian, "User Adaptive QRS Detection Based on One Target Clustering and Correlation Coefficient," 2018 IEEE Biomedical Circuits and Systems Conference (BioCAS), Cleveland, OH, 2018, pp. 1-4, doi: 10.1109/BIOCAS.2018.8584803.

- [9]. Z. Shang, Y. Zhao and Y. Lian, "Removal of Baseline Wander Noise in ECG Signal Using Asymmetrical Frequency-Response Masking Bandpass Filters," 2018 40th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Honolulu, HI, 2018, pp. 6002-6005, doi: 10.1109/EMBC.2018.8513611

- [10]. Z. Shang, Y. Zhao and Y. Lian, "Low power FIR filter design for wearable devices using frequency response masking technique," 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, 2017, pp. 516-519, doi: 10.1109/ASICON.2017.8252526.

- [11]. Z. Shang, Y. Zhao and Y. Lian, "An APWM controlled LLC resonant converter for a wide input range and different load conditions," *2017 IEEE 12th International Conference on ASIC (ASICON)*, Guiyang, 2017, pp. 608-611, doi: 10.1109/ASICON.2017.8252549.

# TABLE OF CONTENTS

| Abstract ii                                                                       |

|-----------------------------------------------------------------------------------|

| Acknowledgements iv                                                               |

| List of Publicationsv                                                             |

| Table of Contents viii                                                            |

| List of Tables xi                                                                 |

| List of Figures xii                                                               |

| List of Acronyms xviii                                                            |

| CHAPTER 1 Introduction                                                            |

| 1.1 Research Motivation1                                                          |

| 1.2 Research Objectives and Dissertation Outline                                  |

| CHAPTER 2 Literature Review                                                       |

| 2.1 Reviews of the Wireless Communication Unit                                    |

| 2.1.1 Wireless Receivers for IoT Sensors                                          |

| 2.1.2 Low-Power Frequency Synthesizers                                            |

| 2.2 Reviews for Power Management Unit for Energy Harvester                        |

| 2.3 Summary                                                                       |

| CHAPTER 3 A Low Power Frequency Tunable FSK Receiver Based on the 4-Path Filter48 |

| 3.1 4-Path Filter based FSK Receiver                                              |

| 3.2 Transient Analysis of Two-Port 4-Path Filter                                  |

|                                                                                   |

| 3.2.1     | Differential Two-Port 4-Path Filter                                    |

|-----------|------------------------------------------------------------------------|

| 3.2.2     | Determine the Data Rate based on the Transient Response60              |

| 3.3 C     | Circuit Design Considerations and Measurement Results for Proposed FSK |

| Receiver  |                                                                        |

| 3.3.1     | Circuit Design Considerations                                          |

| 3.3.2     | Measurement Results                                                    |

| 3.4 C     | Conclusion                                                             |

| CHAPTER 4 | A Low-Power Wide-Locking-Range 4-Path Mixer Based Injection Locking    |

| Frequency | Synthesizer71                                                          |

| 4.1 4     | -Path Mixer Based Injection Locking Frequency Synthesizer71            |

| 4.1.1     | Overall Architecture                                                   |

| 4.1.2     | Locking Range Analysis76                                               |

| 4.2 T     | The Implementation of the Proposed Wide-Locking-Range Frequency        |

| Synthesi  | zer                                                                    |

| 4.2.1     | 5-bit Calibration Circuit                                              |

| 4.2.2     | Digital Controlled Oscillator                                          |

| 4.2.3     | Multi-Input Comparator91                                               |

| 4.3 S     | Simulation Results                                                     |

| 4.4 C     | Conclusion                                                             |

| CHAPTER 5 A  | An 83.9% Efficiency Thermoelectric Energy Harvesting System with OTC- |

|--------------|-----------------------------------------------------------------------|

| PSM Contro   | ol and Low Hardware-Cost MPPT Algorithm101                            |

| 5.1 Sy       | vstem Architecture and Control Strategy103                            |

| 5.1.1        | Proposed System Architecture for Thermoelectric Energy Harvester103   |

| 5.1.2        | OTC-PSM Control Strategy105                                           |

| 5.1.3        | The MPPT Strategy111                                                  |

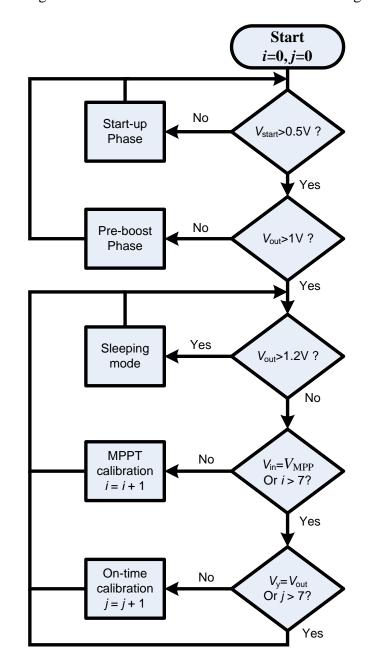

| 5.1.4        | Working Flow of Proposed Converter114                                 |

| 5.2 Ci       | rcuit Implementation119                                               |

| 5.2.1        | Start-Up Circuit                                                      |

| 5.2.2        | Voltage Detector                                                      |

| 5.2.3        | Duty Cycle Generator                                                  |

| 5.2.4        | Register Array and Timing Circuit125                                  |

| 5.3 Ex       | xperimental Results127                                                |

| 5.4 Co       | onclusions133                                                         |

| CHAPTER 6 (  | Conclusions and Future Works134                                       |

| 6.1 Fu       | Ifilled Objectives and Contributions134                               |

| 6.2 Co       | onsiderations for Future Work                                         |

| Bibliography | y140                                                                  |

## LIST OF TABLES

| Table 1-1-1. Features for different types of energy harvester [73]-[76] | 12  |

|-------------------------------------------------------------------------|-----|

| Table 2-1-1 Performance summary of state-of-the-art FSK receiver        | 32  |

| Table 2-1-2 Performance summary for state-of-the-art ILCM               |     |

| Table 2-2-1 Performance summary for state-of-the-art PMU                | 46  |

| Table 3-3-1 FSK receiver performance comparison                         | 69  |

| Table 4-2-1 Truth table of the MUX in the register                      | 86  |

| Table 4-3-1 Performance comparison                                      | 99  |

| Table 5-3-1 Performance comparison                                      | 132 |

## LIST OF FIGURES

| Fig. 1-1-1 Tendency of the number of connected devices worldwide [1]2                         |

|-----------------------------------------------------------------------------------------------|

| Fig. 1-1-2 Tendency of the global market size of IoT [2]2                                     |

| Fig. 1-1-3 Different applications for the WSN based IoT [8]4                                  |

| Fig. 1-1-4 Typical architecture of a wireless sensor                                          |

| Fig. 2-1-1 Architecture of 902-928 MHz ISM band RF receiver [93]17                            |

| Fig. 2-1-2 The block diagram of 0.45V OOK/FSK receiver [97]19                                 |

| Fig. 2-1-3 Architecture for 45µW injection-locked FSK WuRx [102]20                            |

| Fig. 2-1-4 Architecture of N-path filter [116]22                                              |

| Fig. 2-1-5 (a) Switched-RC N-path filter. (b) Single port, single ended N-path filter. (c)    |

| Multiphase clocking. (d) Typical input and output signal [117]24                              |

| Fig. 2-1-6 (a) Single port differential 4-path filter (b) Kernel model for (a)26              |

| Fig. 2-1-7 (a) Theoretical and simulated curve for $H_0(f)$ (b) $H_n(f)$ around the switching |

| frequency for a 4-path filter                                                                 |

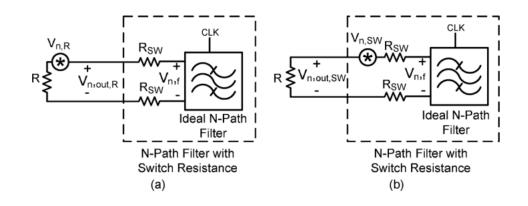

| Fig. 2-1-8 The model for noise calculation. (a) Source noise (b) Switch resistance noise28    |

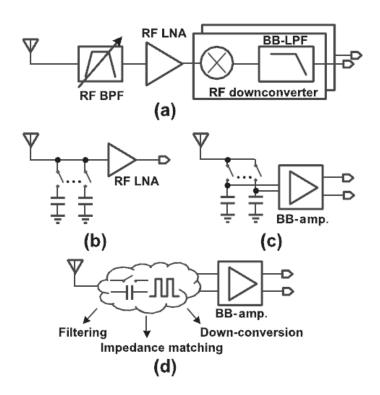

| Fig. 2-1-9 (a) Wideband RX with an off-chip RF bandpass filter (b) Wideband RX front          |

| end with an N-path filter at the RF input (c) mixer-first RX front end (d) Switched           |

| capacitor RX front end                                                                        |

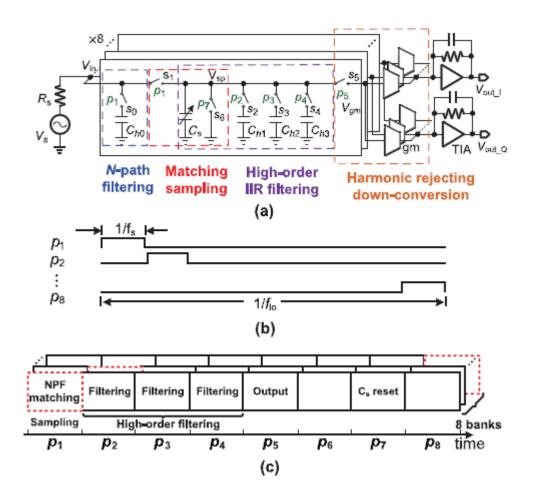

| Fig. 2-1-10 (a) Simplified architecture of a single-ended SC RF front end (b) Clock           |

| waveform (c) Operation of the SC RF front end [128]                                           |

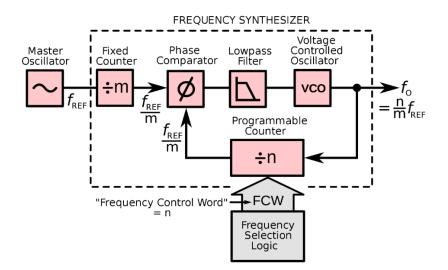

| Fig. 2-1-11 Structure of a PLL-based frequency synthesizer                                    |

|-----------------------------------------------------------------------------------------------|

| Fig. 2-1-12 Architecture of a 0.5V, 440µW frequency synthesizer [131]                         |

| Fig. 2-1-13 Schematic of the VCO in [131]                                                     |

| Fig. 2-1-14 Schematic of the (a) 5-stage ring oscillator and (b) differential delay buffer in |

| [139]                                                                                         |

| Fig. 2-1-15 Equivalent circuit model for a three-stage ring oscillator with multiple-input    |

| injection [142]                                                                               |

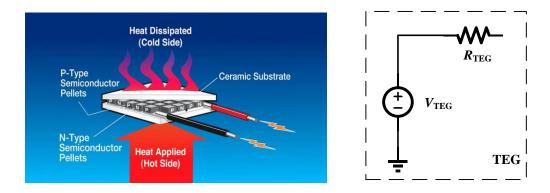

| Fig. 2-2-1 (a) Composition of a TEG. (b) Circuit model of a TEG41                             |

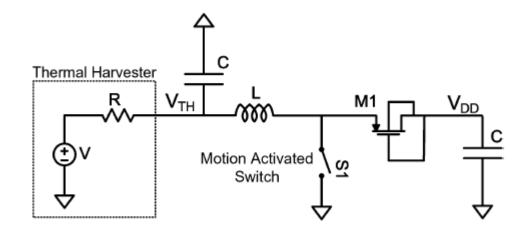

| Fig. 2-2-2 The proposed startup circuit in [156]41                                            |

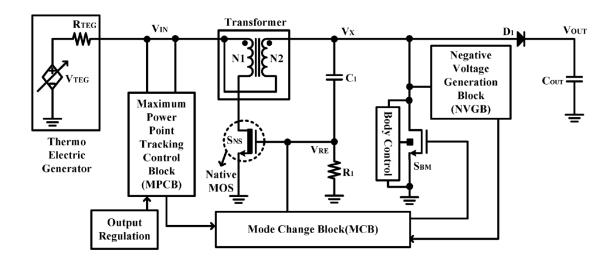

| Fig. 2-2-3 Proposed DC-DC converter architecture in [160]42                                   |

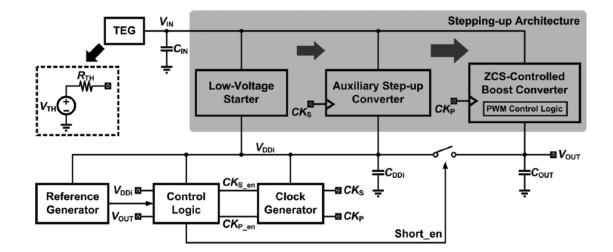

| Fig. 2-2-4 3-stage stepping-up architecture proposed in [161]44                               |

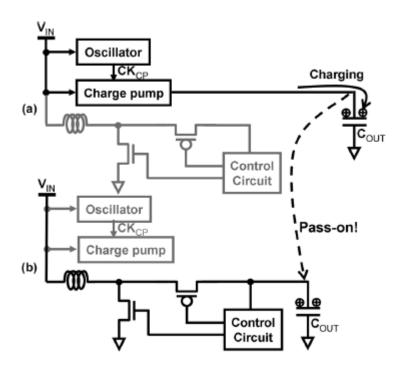

| Fig. 2-2-5 Capacitor pass-on scheme to kick-start the system proposed in [167] (a)            |

| Startup mode (b) Operation mode45                                                             |

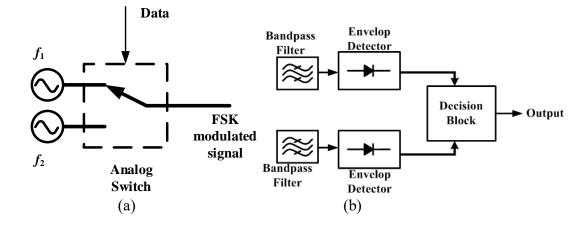

| Fig. 3-1 Conventional structure of FSK (a) modulator and (b) demodulator49                    |

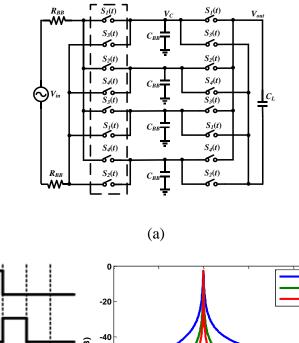

| Fig. 3-2 (a) Differential two-port 4-path filter (b) Clocking scheme for 4-path filter (c)    |

| Frequency response for 4-path filter with different baseband filtering capacitor              |

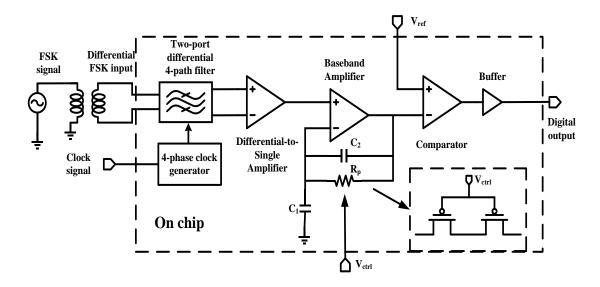

| Fig. 3-1-1 Structure for the proposed 4-path filter based FSK receiver                        |

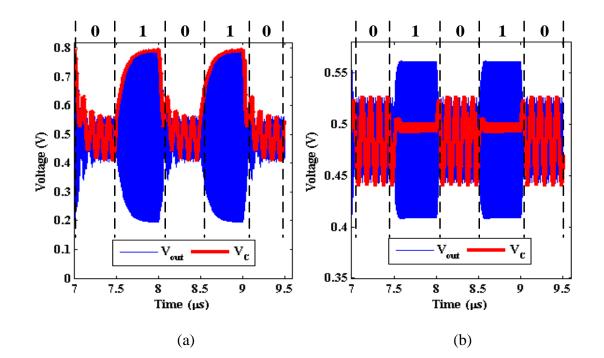

| Fig. 3-2-1 Waveforms of the output voltage and baseband filtering capacitor voltage (a)       |

| with $C_L=80$ fF (b) with $C_L=20$ pF                                                         |

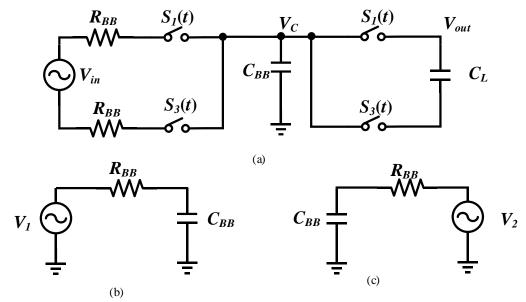

| Fig. 3-2-2 (a) Kernel for differential two-port 4-path filter (b) Simplified circuit when $S_1$                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| connects and (c) Simplified circuit when S <sub>3</sub> connects                                                                                                       |

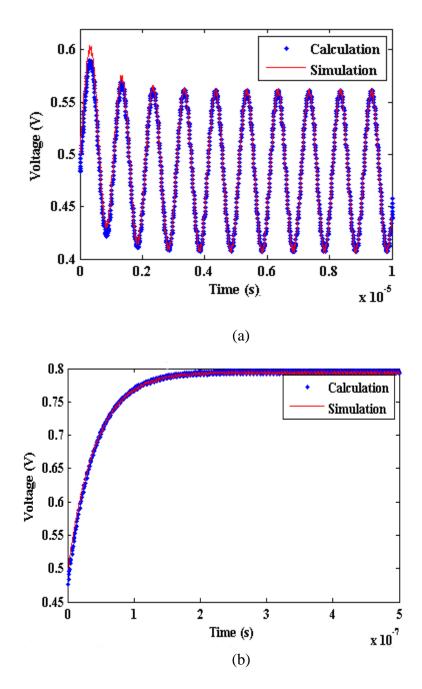

| Fig. 3-2-3 Comparison between the calculation and simulation results for baseband                                                                                      |

| filtering capacitor voltage (a) the input frequency is different from the clock frequency by                                                                           |

| 1MHz (b) the input frequency is equal to the clock frequency                                                                                                           |

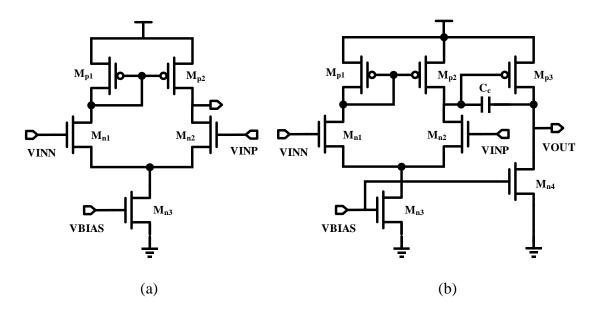

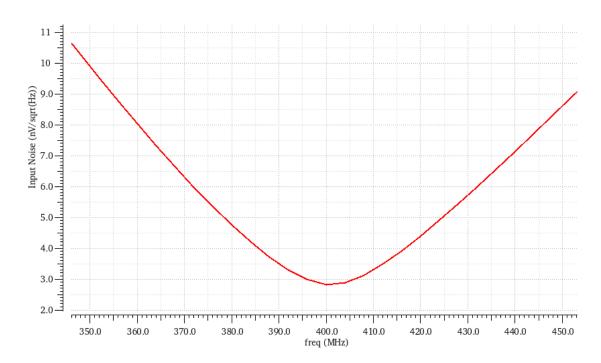

| Fig. 3-3-1 Structure of (a) D2S amplifier and (b) baseband amplifier63                                                                                                 |

| Fig. 3-3-2 Input noise spectrum of 4-path filter and D2S amplifier63                                                                                                   |

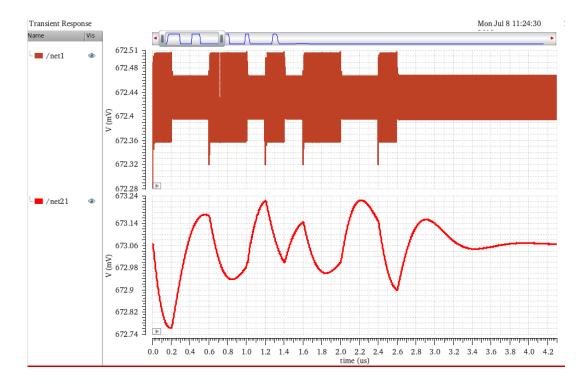

| Fig. 3-3-3 Simulation waveforms for difference frequencies of "01" sequences65                                                                                         |

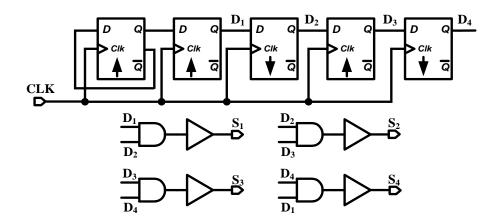

| Fig. 3-3-4 Four-phase non-overlapping clock generator65                                                                                                                |

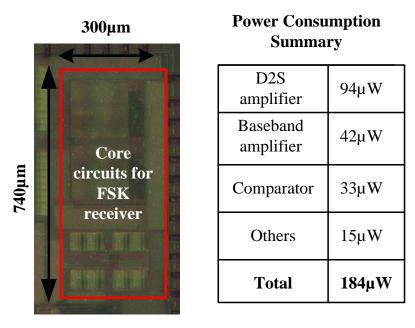

| Fig. 3-3-5 Chip micrograph and power consumption summary67                                                                                                             |

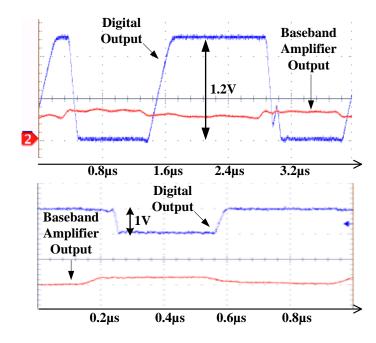

| Fig. 3-3-6 Measured waveform for baseband amplifier output and the system digital                                                                                      |

| output for Case A(top) and Case B(bottom)                                                                                                                              |

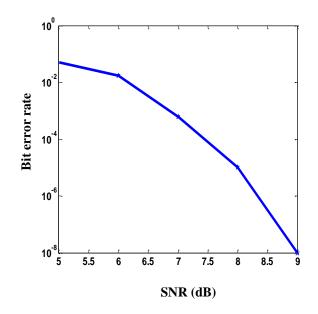

| Fig. 3-3-7 Simulated BER vs SNR plot69                                                                                                                                 |

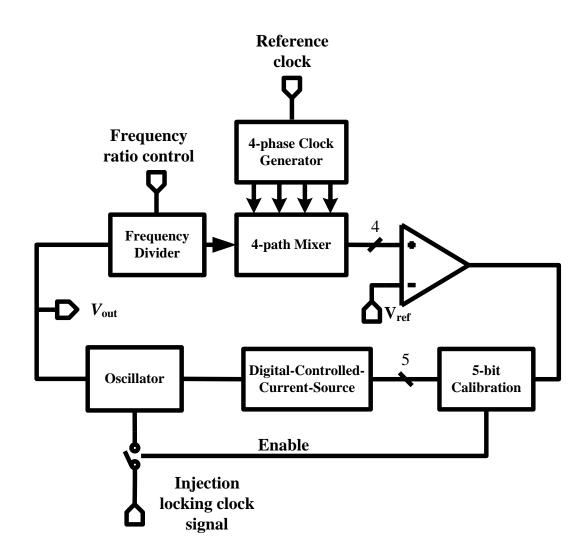

| Fig. 4-1-1 Overall Architecture of the proposed frequency synthesizer74                                                                                                |

| Fig. 4-1-2 (a) Structure of the 4-path mixer (b) Worst case scenario between the input and                                                                             |

| output of the 4-path mixer76                                                                                                                                           |

| Fig. 4-1-3 (a) Simplified model for <i>N</i> -stage ring oscillator without injection (b) Bode                                                                         |

|                                                                                                                                                                        |

| diagram for the <i>RC</i> load (c) Current phasor diagram [62]77                                                                                                       |

| diagram for the <i>RC</i> load (c) Current phasor diagram [62]77<br>Fig. 4-1-4 (a) Simplified model for <i>N</i> -stage ring oscillator with single injection (b) Bode |

| Fig. 4-1-5 The locking mechanism of the proposed 2-step calibration frequency              |

|--------------------------------------------------------------------------------------------|

| synthesizer                                                                                |

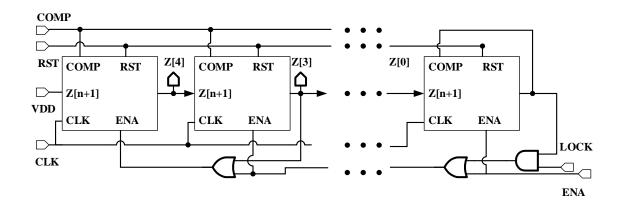

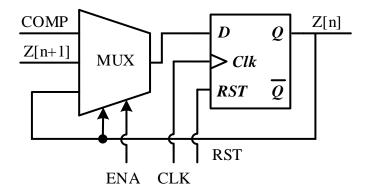

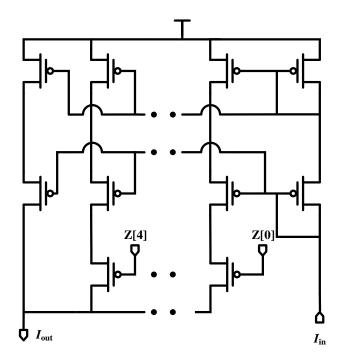

| Fig. 4-2-1 Schematic of the 5-bit successive approximate register                          |

| Fig. 4-2-2 Schematic of the register                                                       |

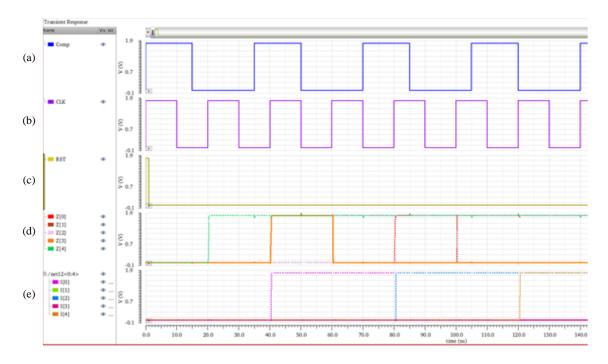

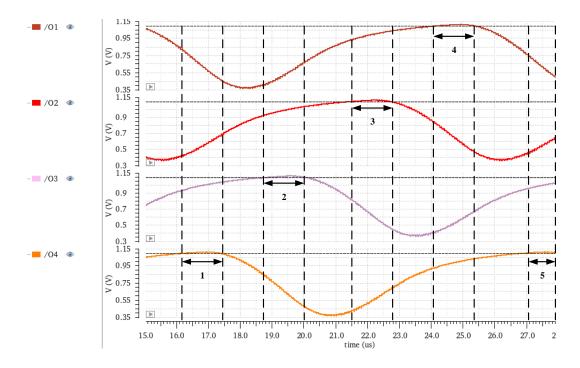

| Fig. 4-2-3 Simulated waveforms of control bits generation (a) Comparison input (b)         |

| Clock signal (c) Reset signal (d) Control bit signal without pulse elimination (e) Control |

| bit signal with pulse elimination                                                          |

| Fig. 4-2-4 3-stage current-starved ring oscillator                                         |

| Fig. 4-2-5 Cascaded 5-bit digital-controlled current source90                              |

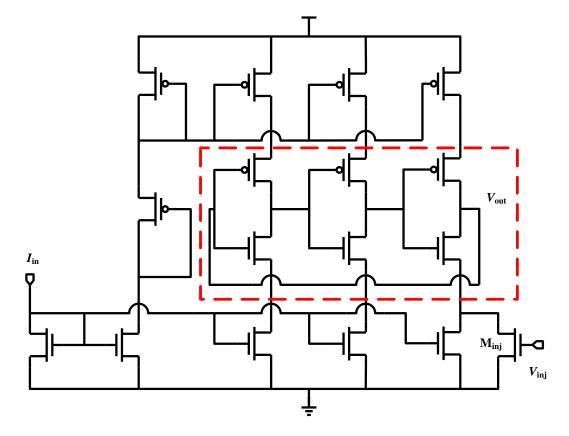

| Fig. 4-2-6 Transient waveform of the output of the 4-path mixer92                          |

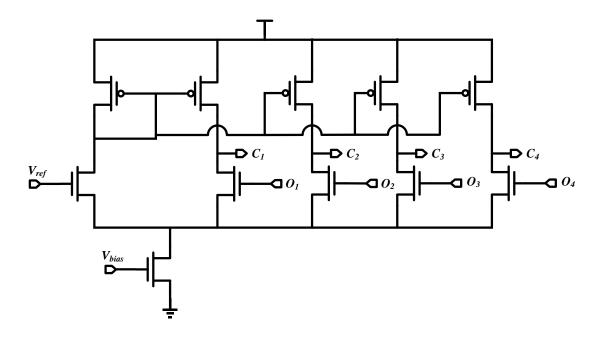

| Fig. 4-2-7 Multi-input comparator                                                          |

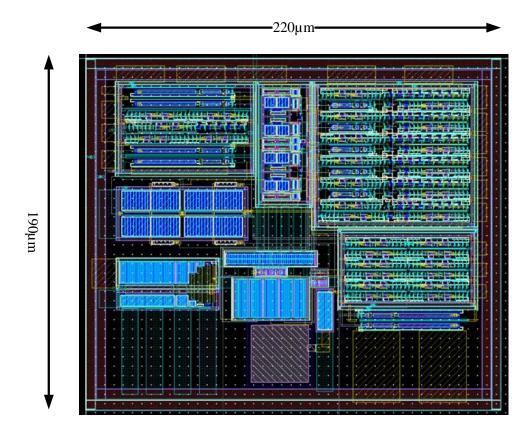

| Fig. 4-3-1 Layout for the core circuit of the proposed frequency synthesizer94             |

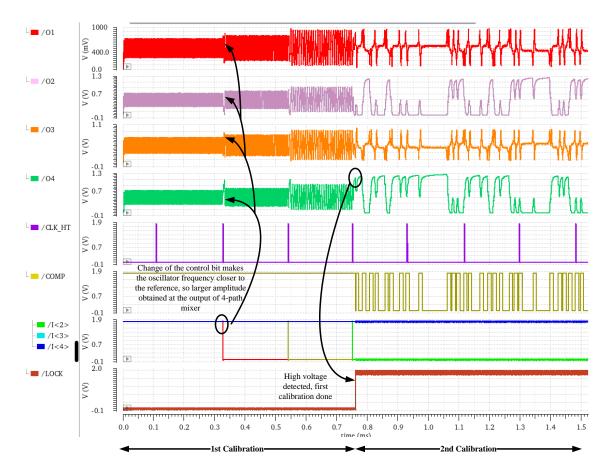

| Fig. 4-3-2 Simulation results for proposed frequency synthesizer                           |

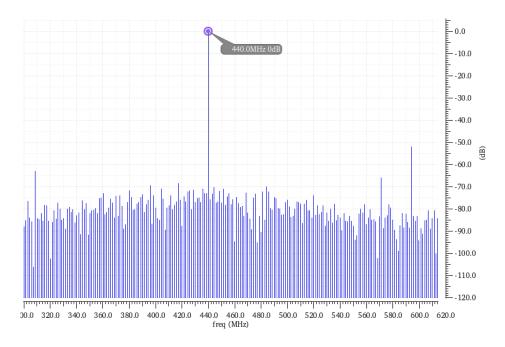

| Fig. 4-3-3 Output spectrum when the frequency synthesize is locked                         |

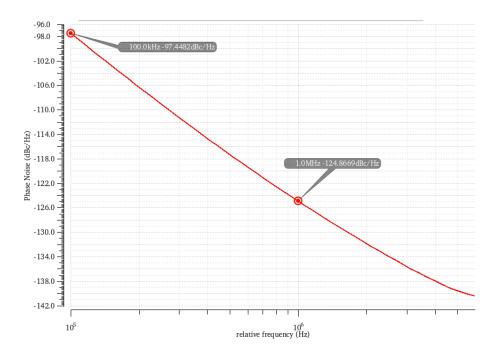

| Fig. 4-3-4 Simulated phase noise of output signal97                                        |

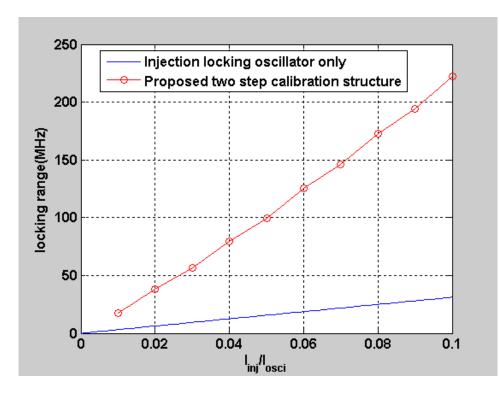

| Fig. 4-3-5 Locking range comparison between the proposed structure and conventional        |

| injection locking                                                                          |

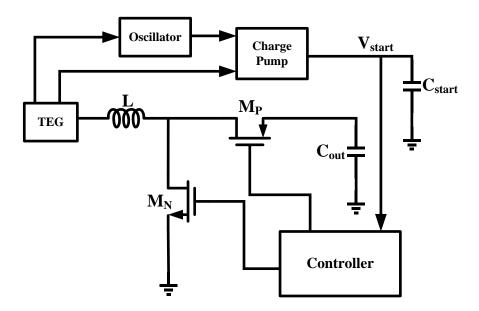

| Fig. 5-1-1 Conventional structure of thermoelectric energy harvester102                    |

| Fig.5-1-2 System architecture of the proposed thermoelectric energy harvester104           |

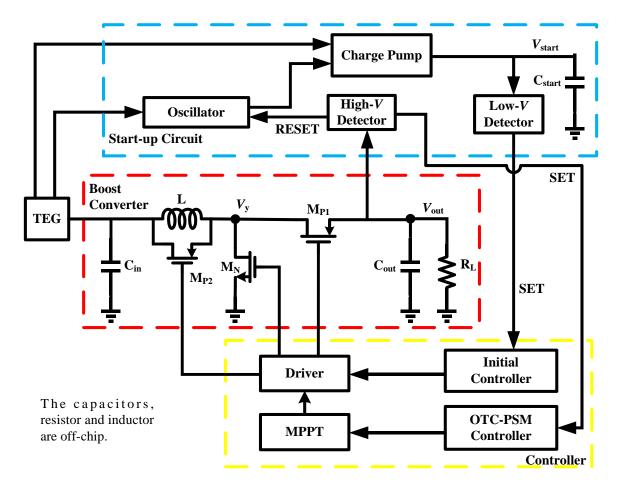

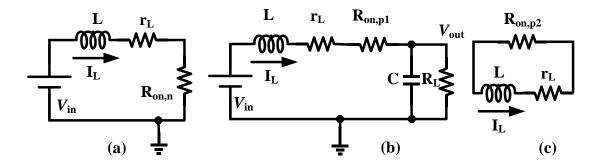

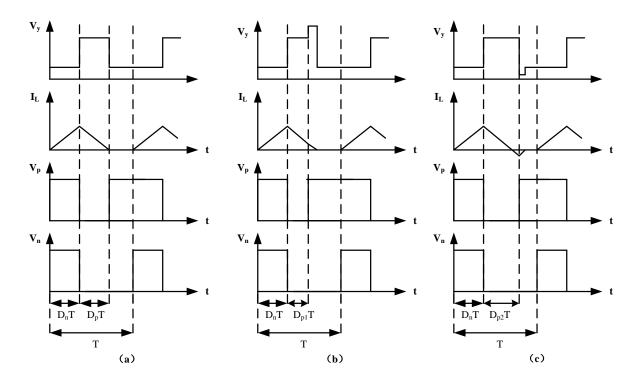

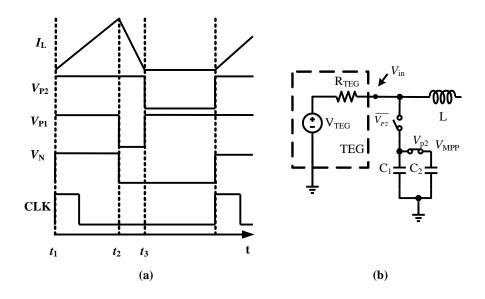

| Fig.5-1-3 Equivalent circuits in different phases of boost converter in DCM (a) on-time             |

|-----------------------------------------------------------------------------------------------------|

| of $M_N(b)$ on-time of $M_{P1}(c)$ on-time of $M_{P2}$ 105                                          |

| Fig. 5-1-4 PMOS turns off (a) at right moment (b) too early and (c) too late107                     |

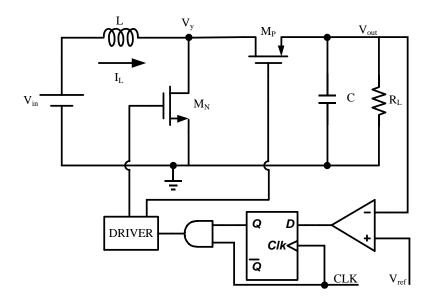

| Fig. 5-1-5 Conventional topology for PSM controlled boost converter108                              |

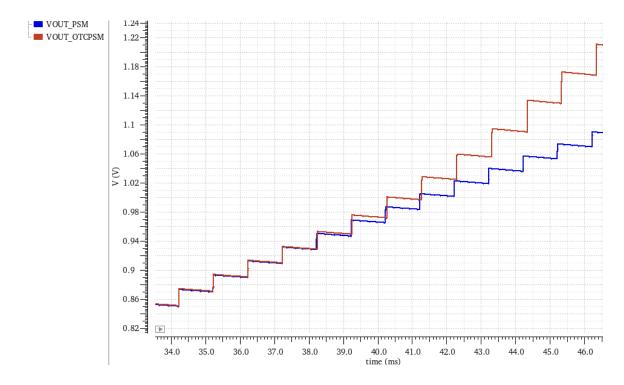

| Fig. 5-1-6 Comparison of the output voltage recovering time between OTC-PSM                         |

| (VOUT_OTCPSM) and traditional PSM (VOUT_PSM)110                                                     |

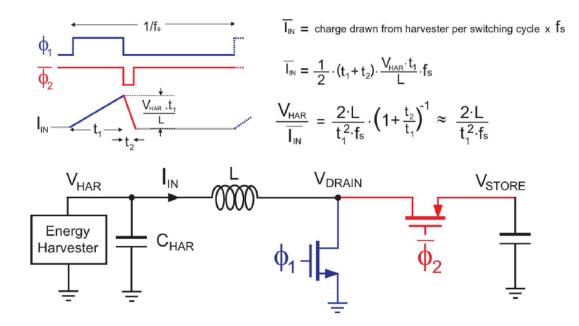

| Fig. 5-1-7 Analysis of the input impedance for a boost converter [74]112                            |

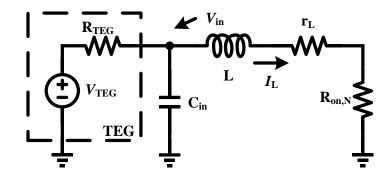

| Fig. 5-1-8 Equivalent circuit of the harvester when $M_N$ is on114                                  |

| Fig. 5-1-9 Working flow of the proposed harvester                                                   |

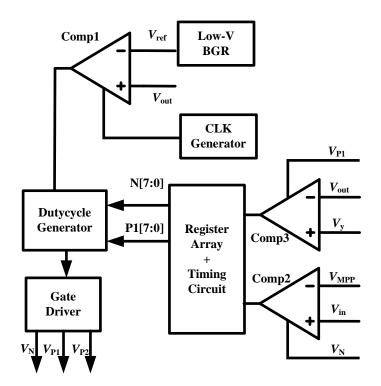

| Fig. 5-1-10 Structure of the proposed controller117                                                 |

| Fig. 5-1-11 (a) Ideal timing diagram for the gate signals and inductor current (b) $V_{\text{TEG}}$ |

| sampler117                                                                                          |

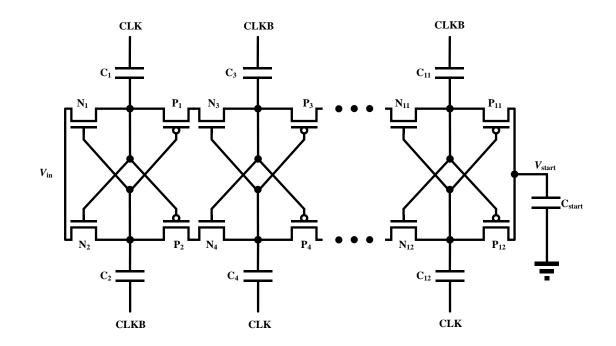

| Fig. 5-2-1 Cross-coupled charge pump119                                                             |

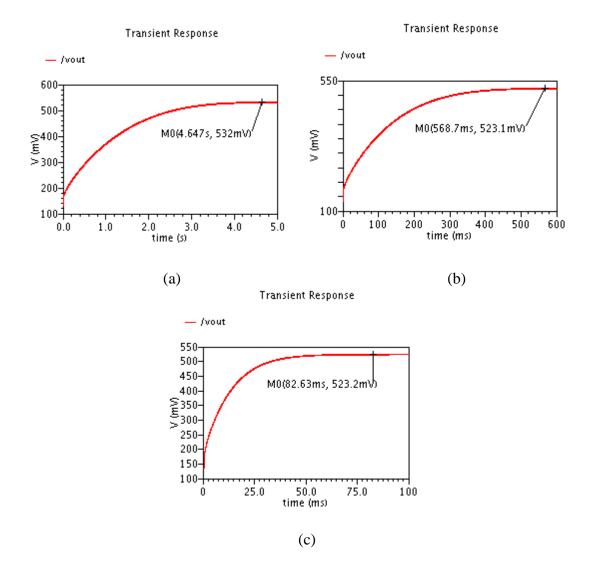

| Fig. 5-2-2 Simulation results for the startup process with 80mV input voltage in (a) slow           |

| corner (b) typical corner and (c) fast corner                                                       |

| Fig. 5-2-3 (a) Low-power reference-less voltage detector (b) Simulated performance for              |

| the voltage detector                                                                                |

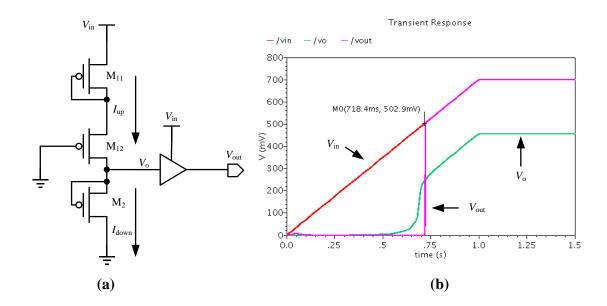

| Fig. 5-2-4 Low power duty cycle generator                                                           |

| Fig. 5-2-5 Simulated performance for the duty cycle generator                                       |

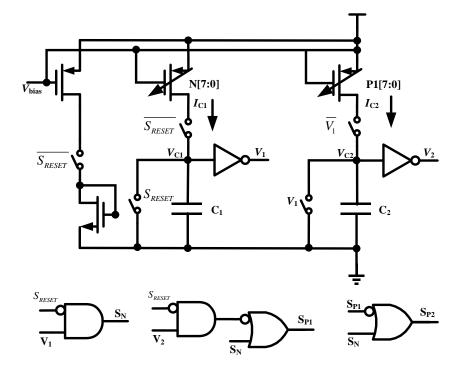

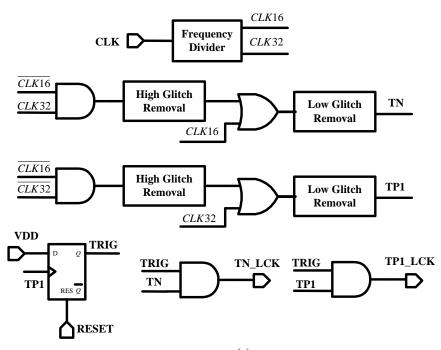

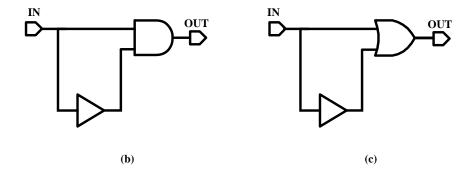

| Fig. 5-2-6 (a) Timing circuits (b) High glitch removal circuit (c) Low glitch removal         |

|-----------------------------------------------------------------------------------------------|

| circuit126                                                                                    |

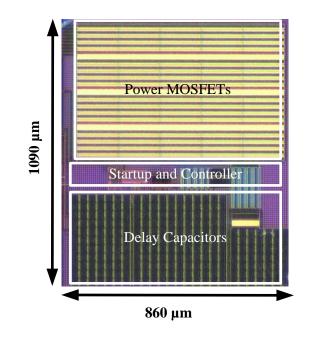

| Fig. 5-3-1 Chip micrograph for the proposed harvester                                         |

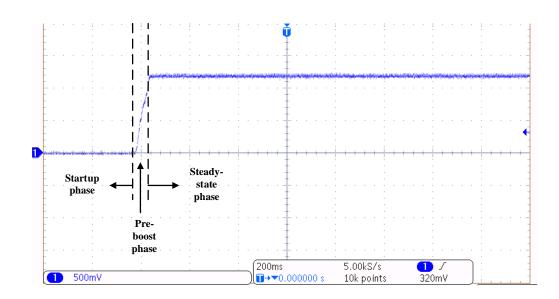

| Fig. 5-3-2 Startup waveform of V <sub>out</sub>                                               |

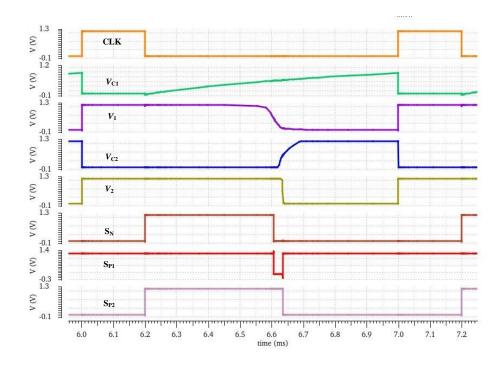

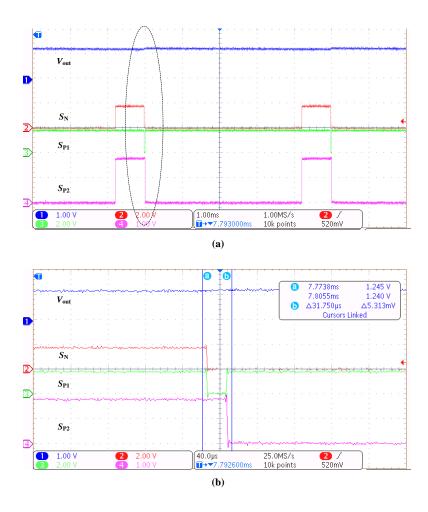

| Fig. 5-3-3 (a) Steady-state waveform of $V_{out}$ and gate signals (b) Zoom in graph centered |

| with S <sub>P1</sub> 129                                                                      |

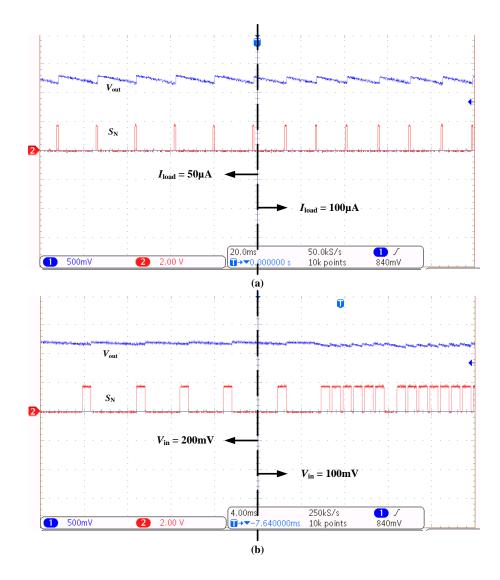

| Fig. 5-3-4 (a) Transient waveform of $V_{out}$ and $S_N$ when load changes (b) Transient      |

| waveform of $V_{out}$ and $S_N$ when input changes                                            |

|                                                                                               |

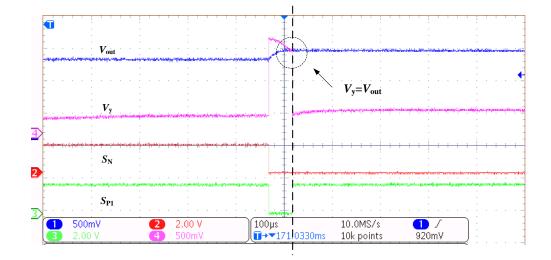

| Fig. 5-3-5 ZCS waveform of V <sub>out</sub> and V <sub>y</sub>                                |

# LIST OF ACRONYMS

| AFC    | Automatic Frequency Calibration                   |

|--------|---------------------------------------------------|

| ASK    | Amplitude Shift Keying                            |

| BB     | Base Band                                         |

| BER    | Bit Error Rate                                    |

| BGR    | Band Gap Reference                                |

| СР     | Charge Pump                                       |

| D2S    | Differential-to-Single-ended                      |

| DCM    | Discontinuous Conduction Mode                     |

| DCO    | Digital Controlled Oscillator                     |

| DMD    | Dual-Mode Demodulator                             |

| DTCMOS | Dynamic Threshold CMOS                            |

| FAC    | Frequency-to-Amplitude Converter                  |

| FSK    | Frequency Shift Keying                            |

| FSPSM  | Folded Semi-Passive Sub-harmonic Mixer            |

| I/Q    | In phase/Quadrature                               |

| ILCM   | Injection Locked Clock Multiplier                 |

| IL-DCO | Injection-Locking Digitally Controlled Oscillator |

| ILO     | Injection-Locked Oscillator                   |

|---------|-----------------------------------------------|

| ILRO    | Injection Locked Ring Oscillator              |

| ІоТ     | Internet of Things                            |

| ISM     | Industrial Scientific and Medical             |

| ITU     | International Telecommunication Union         |

| LNA     | Low Noise Amplifier                           |

| LO      | Local Oscillator                              |

| LPF     | Low-Pass Filter                               |

| LR      | Locking Range                                 |

| LTI     | Linear Time-Invariant                         |

| MCB     | Mode Change Block                             |

| MGLNA   | Multiple-Gated Low-Noise Amplifier            |

| MPPT    | Maximum Power Point Tracking                  |

| OOB     | Out-Of-Band                                   |

| ООК     | On-Off Keying                                 |

| OTC-PSM | On-Time Calibration Pulse Skipping Modulation |

| PA      | Power Amplifier                               |

| PFD     | Phase-Frequency Detector                      |

| PFM     | Pulse Frequency Modulation                    |

| PLL     | Phase-Locked Loop                             |

| PMU  | Power Management Unit           |  |

|------|---------------------------------|--|

| PVT  | Process Voltage and Temperature |  |

| PWM  | Pulse Width Modulation          |  |

| RF   | Radio Frequency                 |  |

| RMS  | Root-Mean-Square                |  |

| SAW  | Surface Acoustic Wave           |  |

| SC   | Switch Capacitor                |  |

| SDC  | Single-to-Differential Circuit  |  |

| SNR  | Signal Noise Ratio              |  |

| TEG  | Thermoelectric Generator        |  |

| VCO  | Voltage-Controlled Oscillator   |  |

| VGA  | Variable Gain Amplifier         |  |

| WBAN | Wireless Body Area Network      |  |

| WSN  | Wireless Sensor Network         |  |

| WUC  | Wake-Up Circuit                 |  |

| WURX | Wake-up Receiver                |  |

| ZCS  | Zero Current Switching          |  |

# Chapter 1 Introduction

#### **1.1 Research Motivation**

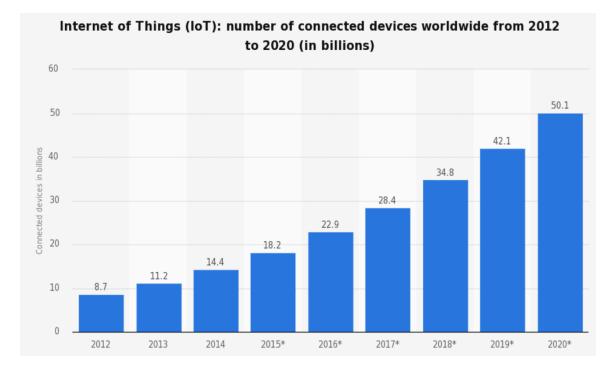

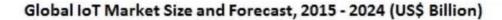

Thanks to the rapid development of the Internet, the Internet of Things (IoT) emerged in 21<sup>st</sup> century and starts changing our daily life. Currently there are already more connected things than people in the world. It is calculated that around 28.4 billion IoT devices were in use in 2017, which was up by 24 percent from that in 2016, and this will likely reach 50.1 billion by the end of 2020 as shown in Fig. 1-1-1 [1]. The IoT market size also exhibits tremendous development currently. The global IoT market is estimated to reach \$1,599T by 2024, from \$346.1B in 2016, attaining a compound annual growth rate of 21.1% from 2016 to 2024 as shown in Fig. 1-1-2 [2].

Extending internet connectivity to everyday objects transforms industry and people's daily life and creates tremendous cost savings. For companies, the IoT technology may provide benefits in several aspects such as improving customer experience, collecting new data, reducing the cost of labour and improving the efficiency. For individuals, IoT can provide them with a more convenient life by connecting more and more things together. For example, thanks to the connected household appliances, people can do the housework by simply touching their smartphones. And IoT can even save people's life by monitoring the vital signs in real time, which means that not only things, but human beings can also be incorporated into the IoT [3][4].

Fig. 1-1-1 Tendency of the number of connected devices worldwide [1]

Fig. 1-1-2 Tendency of the global market size of IoT [2]

There are many kinds of technology involved in IoT applications, such as addressability, secured wireless communication, data processing, software development, etc. Among the different technology categories, hardware takes the biggest part and it costs \$239 billion on modules and sensors, which takes about 50% of the overall IoT market value [5]. Without good sensors, most IoT applications would not exist. This fact makes sensors the critical design component when developing most new IoT applications. Individuals and organizations can use wireless sensors to enable many different kinds of smart applications. From interconnected homes to smart cities, from military to bioengineering, from industry to education, wireless sensors create the infrastructure upon which the IoT comes alive [6][7].

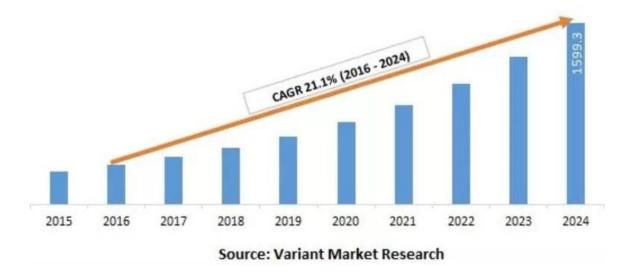

In IoT applications, tons of sensors are distributed across large geographic areas and they together with the central gateway form a wireless sensor network (WSN). Fig. 1-1-3 gives a detailed range of applications of the WSN based IoT and we can see that it covers every aspect in our life [8]. Generally, such network should have some critical characteristics to be considered as a well-designed network, such as the ability to cope with node failures, the scalability to large scale of deployment, the ability to withstand harsh environmental conditions, etc. Some of the characteristics are guaranteed by the network (for example, how to choose among mesh topology or star topology or the combination of them, how to choose the communication protocol between sensor nodes), while others are determined by the sensor node. In this research, we focus on the design of important circuit blocks for wireless sensor nodes.

Fig. 1-1-3 Different applications for the WSN based IoT [8]

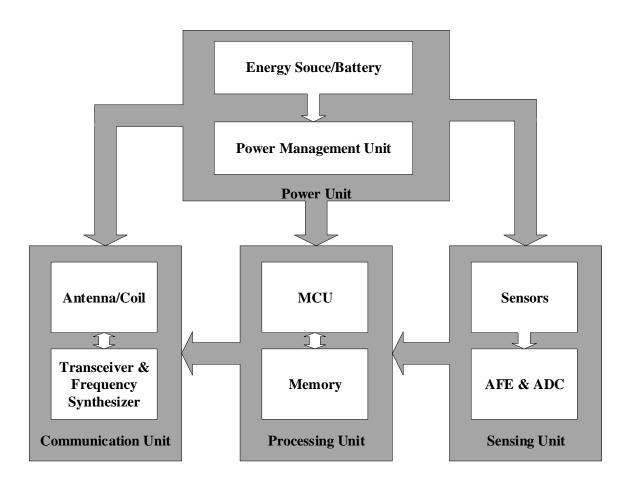

The basic functions of a wireless sensor in IoT applications include obtaining information, processing it, and communicating it to its neighbors. And all the functional blocks should be powered by batteries or an energy harvester. For a better understanding of how these functions are realized, Fig. 1-1-4 gives a typical architecture of a wireless sensor used in IoT applications. As can be seen, it is composed of four basic functional blocks, power unit, sensing unit, processing unit and communication unit [9].

Fig. 1-1-4 Typical architecture of a wireless sensor

Power unit is responsible to supply the other functional blocks with regulated supply voltage and required power. The most common choice for power unit is battery or super-capacitor with high energy density. However, as the wireless sensors in some IoT applications are deployed in a hard-to-reach location, changing the battery or charging the super-capacitor regularly can be costly and inconvenient. So either we extend the lifetime of batteries and super-capacitors by power saving techniques, such as dynamic power management or dynamic voltage scaling to reduce the power consumption of the system [10], or we make the sensor be autonomous by harvesting the surrounding environmental energy [11][12]. Possible energy sources are photovoltaic energy, vibration energy, radio frequency (RF) energy and thermoelectric energy. Each source has its own characteristics and design challenges for the corresponding power management unit, and we will illustrate them in detail in the following sections.

Sensing unit is used to capture data from the environment and to convert the sensed analog signal to digital signal after proper filtering and amplification. Sensors measure physical data such as temperature, pressure, human vital signs, and etc. Analog front end (AFE) is an interface between sensors and analog-digital-converter (ADC) and it is usually composed of filters and amplifiers. ADC is used to convert the AFE processed analog signal to digital signal for the processing unit with proper resolution.

Processing unit processes data and it is usually composed of a microcontroller unit (MCU) and a memory. As the data processing task required within the wireless sensor is usually less complicated, the main considerations for the MCU are low cost and low power consumption, while providing adequate computation power.

Communication unit is used for data exchange with the gateways in the WSN. A transceiver is necessary to modulate/demodulate the digital signal, but it usually consumes the main part of the power budget in wireless sensor, e.g., in [13], the transceiver takes 762µW out of the total 942.9µW power consumption of the wireless sensor SoC. Thus, energy efficient architecture and modulation techniques should be taken into consideration for the design. Also, the carrier frequency of the modulated signal may differ among sensors due to different standard requirement. For example, the industrial, scientific,

medical (ISM) band is commonly used in IoT applications and it differs in different countries, i.e., 433.05MHz to 434.79MHz band is only used in ITU region 1 countries and 902MHz to 928MHz band is only used in region 2 countries [14]. Thus, it's desirable to have a frequency tunable transceiver so that we don't need to customize the transceiver for different frequency bands. A frequency synthesizer is also needed in the communication unit to provide an accurate local oscillation frequency for the transceiver. As the transceiver is supposed to be frequency tunable, the synthesizer shall be able to cover a large frequency range so that it's compatible with the transceiver. Also, the power consumption of the frequency synthesizer should be low.

In general, the wireless sensor should be able to deliver data with high power efficiency. Currently, there are some exciting achievements regarding the wireless sensor design in different IoT applications [13][15]-[21]. In [13], a CMOS multi-sensor SoC capable of reconfiguration, self powering, signal processing and wireless communication is presented for real-time human vital sign monitoring. The proposed SoC can monitor four physiological parameters (temperature, glucose/protein concentration and pH value) simultaneously and it consumes only 942.9 $\mu$ W. Despite the AFE, ADC and wireless transmitter, the SoC has an embedded energy harvesting interface which can gather light energy and RF energy. However, its energy conversion efficiency is only 73% and its wireless carrier frequency is fixed. In [15], the authors proposed a single-chip sensor node IC for continuous and real-time ECG monitoring. The authors focused on the design of the AFE,  $\Delta\Sigma$ ADC and on-off keying (OOK) transmitter. The AFE has a programmable gain from 38 to 58dB, a bandwidth from 0.1 to 300Hz and a total integrated input referred noise as 18.7 $\mu$ V. The ADC has an ENOB as 10bits and it consumes 71 $\mu$ A with 0.7V voltage supply. The OOK transmitter consumes 670 $\mu$ W at 433.92MHz carrier frequency and 19.2kbps to 1Mbps data rate. However, a critical component is missing from this design, i.e. no wireless receiver is integrated in the sensor chip. Without a receiver, the sensor won't be able to collaborate with other sensor nodes in the WSN. In [20], a 70 $\mu$ W 1.19mm<sup>2</sup> wireless sensor SoC with 32 channels of resistive and capacitive sensors is presented, which can be applied in various IoT scenarios, such as environmental monitoring, wearable and human-computer interaction. A novel CDMA-like resistance/capacitance-to-voltage converter and a single-slope ADC form the sensing unit in the SoC and its communication unit applies an edge-encoded PWM UWB transceiver for low power consumption. However, the SoC lacks power unit and the UWB transceiver occupies a large bandwidth despite of the low power feature.

By reviewing the state-of-art wireless sensor SoCs, we see that there is less motivation to focus on the processing unit as the local data processing load is not heavy. While all the other three functional blocks of the wireless sensor draw attention of the researchers, the sensing unit may have different requirements according to the sensed parameter. For example, the required AFE bandwidth for ECG in [15] is different from that for other physiological parameters in [13]. In contrast, the power and communication units can be designed to be generally suited for different wireless sensors. And such universality can reduce the cost comparing to the customized design. Therefore, in this research, we will focus on the design for power and communication units. Note that even the transmitter and receiver are both important for wireless sensor, we focus on the receiver design in this research mainly because that the it is considered more challenging than transmitter design, especially for low power design.

There are many researchers focusing on the receiver [22]-[30] and frequency synthesizer [31]-[36] design and good performances have been achieved. In recent studies, frequency shift keying (FSK) shows a high-transmission efficiency. Meanwhile, it is less susceptible to frequency pulling due to its constant envelop nature, thus, it has better noise immunity at very low power levels [22][23]. By combining sliding-IF based low-power down-conversion and relative-power-detection based FSK demodulation, the proposed receiver in [25] achieves -102dBm sensitivity with 0.6V supply voltage and 466µW power consumption. In [28], a dual injection locked FSK-to-ASK conversion technique is proposed and the FSK receiver achieves -78dBm sensitivity for 8Mbps data rate while consuming 639µW power. A ring-type voltage-controlled oscillator based frequency synthesizer is proposed in [33]. Thanks to the injection locking and frequency tracking loop techniques, the frequency synthesizer achieves -115dBc/Hz in-band phase noise and 370µW power consumption. However, despite the achievements, there are still some challenges in the design of the communication unit.

First, frequency tunability is highly desired for the receiver to adapt different IoT application scenarios and standards, but it's challenging to design a low power frequency tunable receiver [37]-[42]. The core component for tunable receivers is bandpass filter

whose center frequency can be easily changed. One solution is to use an array of dedicated, bulky, off-chip and non-tunable filters such as surface acoustic wave (SAW) filters [43]-[45]. However, such off-chip solution may take considerable amount of area. State-of-theart research proposes some on-chip solutions such as LC filters [46]-[49] and  $G_m$ -C filters [50]-[53]. However, LC filters suffer from low quality factor due to the inductor and limited tunability due to the varactor, while  $G_m$ -C filters need to trade off among power consumption, quality factor and center frequency and they usually require additional tuning circuitry. Thus, direct tunable integrated bandpass filter with high Q factor is critical for the tunable receiver design.

Second, it's hard to design a frequency synthesizer achieving low power consumption and large locking range simultaneously. As the frequency synthesizer needs to provide local oscillation frequency to the tunable receiver, it needs to cover a large frequency range based on the receiver requirement. There are two commonly used techniques for the frequency synthesizer, i.e., phase locked loop (PLL) and injection locking (IL). The PLL based synthesizer has the potential to cover a larger frequency range at the cost of more complicated structure as well as more power consumption [54]-[57]. On the other hand, the IL based synthesizer is easier to implement but it suffers from limited locking range [58]-[60]. Recently, multi-phase injection technique is proposed to enlarge the locking range [61]-[65] and a 23.6% locking range with center frequency at 14.85GHz has been achieved, but it requires accurate phase control of the injected signal, which in turn needs more sophisticated control circuits and higher power consumption, i.e.,

1.56mW [63]. Thus, a frequency synthesizer with low power consumption and large locking range is desired.

Except the two specific requirements for the communication unit of IoT wireless sensor, other general requirements shall also be taken into consideration, i.e., high sensitivity for the FSK receiver and low phase noise for the frequency synthesizer.

Another aspect for the wireless sensor which we will focus on and try to make it generally adaptive is the power management unit (PMU). As discussed, batteries are the conventional choice, but it requires charge or change regularly and occupies large area, which translates to high cost in some IoT applications as the location of the sensors are widely spread and hard to reach. As the power consumption of the sensor interfaces have been reduced dramatically thanks to the recent advance in CMOS technology, powering the sensors by environmental energy harvesters becomes possible [66]-[68].

To harvest environmental surrounding energy, several different kinds of energy harvesters have been applied, such as photovoltaic energy harvester, vibration energy harvester, RF energy harvester and thermoelectric energy harvester [69]-[72]. The features are concluded in Table 1-1-1, including the typical output impedance of the energy source, the typical output voltage and power as well as the main design challenges [73]-[76]. The energy source shall be selected according to the application requirement, such as the availability of the energy, the chip area and power budget, etc. In [77], a multi-input dual-output architecture is proposed to harvest energy from photovoltaic, thermoelectric and piezoelectric all at the same time with a single inductor. Even though such system is more

reliable due to multiple energy sources, the sharing inductor and complicated control block limits the overall energy efficiency. Actually, most of the researchers focus on the harvester design and optimization for a single energy source.

| Energy<br>Source  | Challenges                                                       | Typical<br>Electrical<br>Impedance                                     | Typical Voltage                                               | Typical Power<br>Output                                              |

|-------------------|------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|

| Light/Solar       | Conform to small<br>surface area;<br>Wide input<br>voltage range | Varies with light input:<br>Low $k\Omega$ to tens of $k\Omega$         | DC: 0.5V to 5V<br>(Depends on<br>number of cells<br>in array) | 10μW – 15mW<br>(Outdoors:<br>0.15mW –<br>15mW<br>Indoors:<br><500μW) |

| Vibrational       | Variability of<br>vibrational<br>frequency                       | Constant<br>impedance<br>tens of $k\Omega$ to<br>hundreds of $k\Omega$ | AC: tens of volts                                             | $1 \ \mu W - 20 mW$                                                  |

| Thermal           | Small thermal<br>gradients;<br>Efficient heat<br>sinking         | Constant<br>impedance:<br>$1\Omega$ to hundreds<br>of $\Omega$         | DC: tens of<br>millivolts to<br>volts                         | 0.5mW –<br>10mW<br>(20°C gradient)                                   |

| RF &<br>Inductive | Coupling & rectification                                         | Constant<br>impedance<br>Low kΩ                                        | AC: Varies with distance and power $0.5V - 5V$                | Wide range                                                           |

Table 1-1-1. Features for different types of energy harvester [73]-[76]

After the selection of energy source, a regulator, usually a DC-DC converter, is needed to regulate the output voltage and power so that provides stable voltages to different units in a sensor. According to different energy source, there are various requirements for the regulator. For example, for vibrational and RF energy, a rectifier is necessary before the DC-DC converter [78][79], while for thermoelectric energy, a low voltage start up 12

circuit is mandatory [80]-[82]. And there are also some common considerations regardless the energy sources, such as maximum power point tracking (MPPT), reducing conduction loss, switching loss and power optimization for the control block [83][84].

In summary, this research will focus on the design of wireless communication circuits, i.e., receiver and frequency synthesizer, and autonomous power management unit for wireless sensor in IoT applications, aiming to solve the challenges described above.

#### **1.2** Research Objectives and Dissertation Outline

The objectives of this research are set as follows based on the discussion in Section 1.1.

For the communication unit, a low-power, frequency tunable FSK receiver shall be implemented with the help of a fully integrated, center frequency tunable band-pass filter. This filter will make our receiver be able to handle the RF input signals located in different frequency bands, especially for FSK modulation schemes. Secondly, we need to design a low-power low-phase-noise frequency synthesizer with large locking range to provide an accurate reference clock signal to the receiver.

For the power unit, we need to design a power management unit (PMU) which can provide a regulated stable output voltage. Meanwhile, it should have MPPT function and the energy conversion efficiency should be optimized.

In this research, we proposed several techniques to achieve these goals, and the rest of the dissertation is organized as follows.

The literature review and current research progress on FSK receivers, frequency synthesizers and energy harvesters are presented in Chapter 2.

In Chapter 3, a novel 4-path filter based tunable FSK receiver is presented. We have derived the transient response of the 4-path filter with two-tone inputs and this can help us to determine the maximum achievable data-rate. A fully integrated tunable FSK receiver based on 4-path filter has been implemented in  $0.13\mu$ m CMOS process. The chip occupies  $300 \times 700\mu$ m<sup>2</sup>, achieves data rate of 2.5Mbps, and 74pJ/bit Energy per Bit at -65 dBm sensitivity [85].

In Chapter 4, we present a novel frequency synthesizer based on 4-path mixer and injection-locking. The proposed frequency synthesizer has a two-step tracking mechanism. The first step (coarse tracking) is accomplished by the 4-path mixer and the second step (fine tracking) is done by the injection-locking technique. The tracking ranges of the two steps are also analyzed. This design is implemented in 0.18 $\mu$ m CMOS process. The core circuit occupies 220 $\mu$ m x 190 $\mu$ m. The simulation results show that it can successfully lock the output frequency at 4440MHz of a free-running 3 stage ring oscillator with a power consumption as 305 $\mu$ W. The phase noise at 1MHz offset is -124.86dBc/Hz and it is -97.45dBc/Hz at 100kHz offset. And the integrated RMS jitter from 10kHz to 40MHz is 2.5ps.

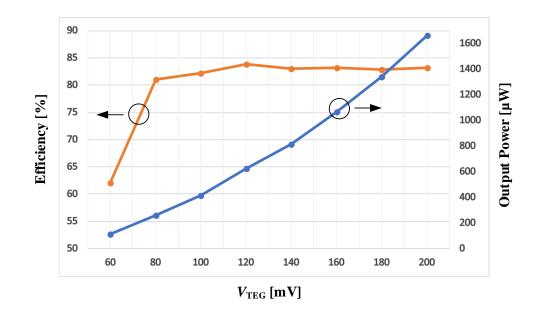

In Chapter 5, a boost converter with high efficiency for thermo-electrical energy generator (TEG) is presented as an example for the energy harvester PMU design for wireless sensor. An on-time calibration based pulse skipping modulation (OTC-PSM) scheme is proposed to reduce the power of the controller. A hardware-efficient maximum power point tracking (MPPT) circuit is introduced for the constant internal resistance source of TEG. The proposed design has been implemented in a standard 180nm CMOS process, achieving a high efficiency of 83.9% at 120mV input voltage and output power of  $600\mu$ W. The proposed OTC-PSM scheme saves considerable power in achieving 83.9% efficiency as well as low output ripple as 5mV. Also, the proposed MPPT is simple and easy to implement for low cost [86].

The conclusion and considerations for future works are given in Chapter 6.

# Chapter 2 Literature Review

In this chapter, we present the literature reviews of the communication unit and power management unit for IoT wireless sensors. In Section 2.1, reviews for receiver and frequency synthesizer are given. In Section 2.2, thermoelectric energy harvesting systems are reviewed. The summary is given in Section 2.3.

#### 2.1 **Reviews of the Wireless Communication Unit**

The objectives in section 1.2 indicate that we need to design an FSK receiver and a frequency synthesizer for the communication unit of the wireless sensor. We present literature reviews for receiver and frequency synthesizer in this section.

#### 2.1.1 Wireless Receivers for IoT Sensors

The first consideration for receiver design in IoT wireless sensors is reducing the power consumption. Therefore, simple modulation schemes are widely used in such applications, like OOK and FSK. The demodulators for them need less functional blocks and are easier to save power [87]-[92]. Meanwhile, the sensitivity and data rate of the receiver should also be optimized while maintaining low power consumption. Comparing to OOK, FSK shows better transmission efficiency and noise immunity. Thus, it attracts more and more attention from the researchers. Several novel techniques are proposed to save power of the FSK receiver while keeping a good sensitivity and data rate, such as injection-locking

frequency-to-amplitude converter [93]-[96], wake-up mechanism [97]-[101], digitally calibrated injection locking oscillator [102][103], etc. In this section, we review some state-of-the-art techniques for FSK receiver.

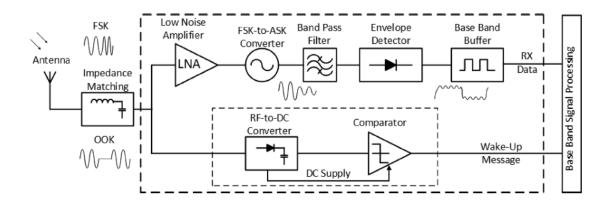

In [93], an ultra-low power ISM band RF receiver for IoT devices is proposed. Its overall architecture is shown in Fig. 2-1-1.

Fig. 2-1-1 Architecture of 902-928 MHz ISM band RF receiver [93]

The receiver is composed of two channels, a primary communication channel and a secondary wake-up receiver channel. During standby period when no data is communicated, the primary channel is disabled, and the ultra-low-power secondary channel will wake up the primary channel when a wake-up message is detected. The primary receiver demodulates FSK signal. The received FSK signal is firstly amplified by the low-noise-amplifier (LNA) and then the amplified signal is fed into the frequency-toamplitude converter (FAC). Through the FAC, the frequency difference is converted to amplitude difference and the signal is now amplitude shift keying (ASK) modulated. Challenges for ISM receivers are mainly the noise and the interferences, thus, a narrow BPF is used to further remove the out-of-band blockers and to improve the frequency selectivity of the receiver. Envelope detector and baseband buffer are applied to obtain a demodulated data. The proposed receiver can handle FSK signals with high data-rate of several mega bits per second (bps). Thanks to the FAC, an easily implemented ASK receiver can be used. And such topology successfully eliminates the need of a local oscillator and I/Q signal path, which requires more circuit components and more power. In addition, the FAC also provides additional gain to the signal and this can relax the design requirement for the LNA.

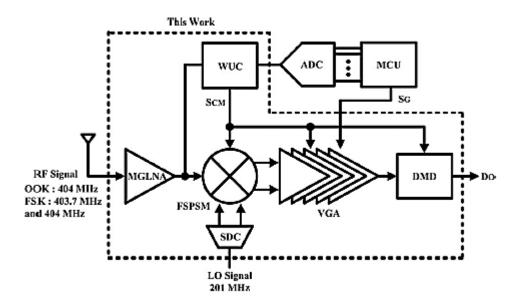

In [97], a 0.45V low-power receiver which utilizes a wake-up mechanism to adjust its power consumption automatically is proposed. The receiver architecture is shown in Fig. 2-1-2.

This receiver consists of a multiple-gated low-noise amplifier (MGLNA), a wakeup circuit (WUC), a folded semi-passive sub-harmonic mixer (FSPSM), a variable-gain amplifier (VGA), a dual-mode demodulator (DMD) and a single-to-differential circuit (SDC).

Because the receiver works under 0.45V supply, which is lower than the normal threshold voltage of the CMOS transistor, the forward body biasing is applied to every transistor in order to lower the threshold voltage. WUC is used to detect the RF signal amplitude and to further control SCM to adjust the power consumptions of other blocks automatically. The noise figure of the overall receiver is mainly determined by the MGLNA, which is the first stage. In addition to the high gain for the purpose of good noise

performance, the MGLNA also adopts a linearity-improving technique, which is important because poor linearity may lead to the WUC to generate wrong control signal. Besides, the gain of the MGLNA can help to improve sensitivity of the WUC. The output of FSPSM is fed into the VGA, whose voltage gain is adjusted by an off-chip ADC and an MCU. After amplification by the VGA, the signal can be demodulated by the DMD.

Fig. 2-1-2 The block diagram of 0.45V OOK/FSK receiver [97]

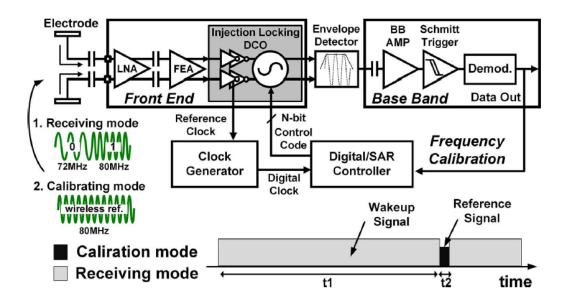

A dedicated ultra-low power fully integrated FSK wake-up receiver (WuRx) for wireless body area network is proposed in [102]. Fig. 2-1-3 shows its overall architecture.

The core blocks of this WuRx are front-end circuits, an injection-locking digitally controlled oscillator (IL-DCO), an envelope detector, baseband circuits and an autocalibration loop with a successive approximated register (SAR) controller. The IL-DCO is most critical as it can convert the frequency difference to the amplitude difference and provide some amplification gain at the same time. In addition, by locating it between the front-end circuits and the envelop detector, it acts as an isolator to reduce the noise effect from the envelope detector to the front-end. The receiver operates in two modes, i.e., receiving mode and calibrating mode, according to whether the received signal is FSK modulated or not and whether the closed loop for frequency calibration is activated or not.

Fig. 2-1-3 Architecture for 45µW injection-locked FSK WuRx [102]

As depicted in Fig. 2-1-3, the receiving mode happens during the time period of  $t_1$ . The input signal is FSK modulated, whose frequencies are 72 MHz and 80 MHz with a data rate as 312 kb/s. The input signal is firstly amplified by the front-end circuits and then is fed into the IL-DCO. The locking range of the IL-DCO is centered at 80 MHz and therefore, it will be injection-locked by the 80 MHz and be injection-pulled by the 72 MHz. As a result, the two frequencies will have different amplitude and the signal is now like an ASK signal. Then, the envelope detector takes the ASK signal as input and remove the carrier frequencies. The baseband circuits further amplify the amplitude difference, and as a result, a demodulated RX signal can be obtained. In this mode, the calibration signal is not valid, and the digital/SAR controller doesn't work.

On the other hand, in the calibrating mode during the time period of  $t_2$ , the input signal is an accurate 80 MHz sinusoidal signal. And the frequency calibration loop is enabled to tune the oscillation frequency by changing the control code of the IL-DCO. Ideally, the IL-DCO should be locked at 80 MHz after the calibration is finished.

From above review, we noted that the core block for an FSK receiver is the frequency-to-amplitude converter. [93] and [102] implement such converter with injection locking oscillator, however, the limited locking range of the oscillator requires that the two carrier frequencies should be located at a distance, otherwise, the carrier frequencies will be both injection locked and no data can be extracted. And this means more bandwidth occupancy for FSK modulation. [97] achieves the frequency-to-amplitude conversion by using mixer, however, such approach needs further processing by the VGA and ADC.

Actually, the most convenient way of converting the frequency difference to amplitude difference for FSK demodulation is to use a high-Q bandpass filter centered at one of the carrier frequencies. However, such method is less attractive for integrated solution due to the limitations of the bandpass filter, either off-chip (SAW filter) or on-chip (LC filter and G<sub>m</sub>-C filter), as discussed in Chapter 1. Fortunately, N-path filter, which is composed of multiple identical low-pass filters and switches, is a promising candidate

to satisfy the requirements for on-chip band-pass filter to serve as the frequency-toamplitude converter in FSK demodulation. N-path filters have interesting features such as direct tunability with the switching frequency, potential higher *Q*-factors, high linearity and graceful scaling with process [104]-[115].

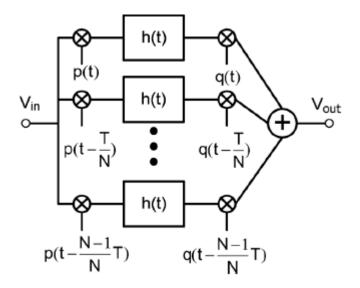

The concept of N-path configuration was firstly proposed by [116] in 1960 and its architecture is shown in Fig. 2-1-4.

Fig. 2-1-4 Architecture of N-path filter [116]

The N-path filter is composed of *N* identical linear time-invariant (LTI) blocks whose impulse response is h(t) and 2*N* frequency mixers, which are driven by time shifted clocks p(t) and q(t). For two adjacent branches, the shifted time is *N*/*T*, where *T* is the period of mixer clock. Let the LTI block be a low-pass filter, the general N-path filter will behave as a band-pass filter with center frequency as mixing frequency. Actually, the first series of mixers who are driven by p(t), p(t-T/N), ..., p(t-(N-1)T/N) are used to down-convert the input signal to baseband from its original band, which can be at a high frequency. Then the LTI block or low-pass filter will process this signal and another series of mixers driven by q(t), q(t-T/N), ..., q(t-(N-1)T/N) will up-convert it back to its original band. The combination of a high mixing frequency and a narrow low-pass filter bandwidth will return a very high Q of this kind of N-path band-pass filter.

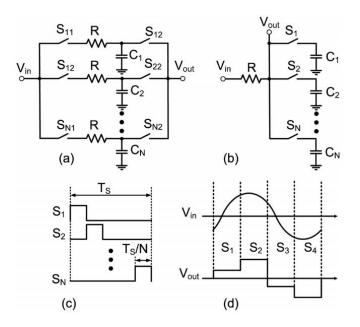

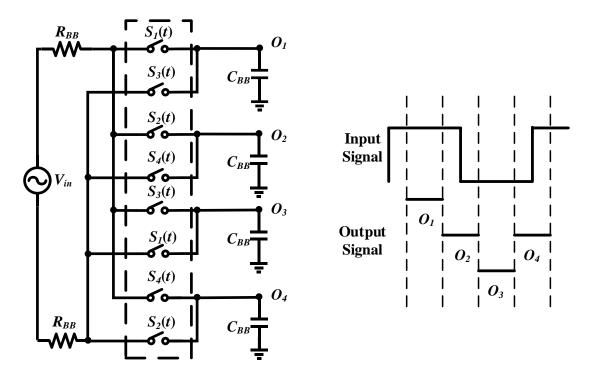

In Fig. 2-1-5(a), we replace the LTI block and mixer with RC low-pass filter and MOS switches respectively. Fig. 2-1-5(c) shows the multi-phase clocking scheme for the switches, and it's clear that the on-time for switches in different branches should be non-overlapping. Ideally, there should not be any moment in which the capacitors can share charge. Due to this fact as well as the memory-less property of resistors, we can simplify the circuit in Fig. 2-1-5(a) to Fig. 2-1-5(b), where only one resistor is used and shared with all the *N* branches. Moreover, since the clocks for switches  $S_{n1}$  and  $S_{n2}$ , where  $1 \le n \le N$ , are the same, so we can use only one series of switches to realize the functions of two as shown in Fig. 2-1-5(b) and the output will be available between the shared resistor and the switches [117].

Since the switches in N-path filter are non-overlapping, one and only one capacitor is connected to the output node at any moment. Assuming that  $RC >> T_s/N$ , during each time interval  $T_s/N$ , the output voltage  $V_{out}$  will be the average of the input voltage  $V_{in}$ . If the input frequency is the same as the switching frequency, for a certain branch, the same part of input voltage will be averaged by the same RC circuit for every period. Thus, the output will be stable and is a staircase approximation as shown in Fig. 4(d) (assuming that N=4). In this case, the average voltage across each capacitor for different period keeps the same. Therefore, the capacitors conduct no current. However, if the input frequency  $f_{in}$  is not the same as the switching frequency  $f_s$ , for a single capacitor, the average voltage across it will change period by period, and its beat frequency is given by  $\Delta f = |f_{in} - f_s|$ . Thus, the capacitors conduct current while switches are on and the average voltage on the capacitors will tend to zero. Therefore, input signals whose frequency is above or below the switching frequency will be suppressed.

Fig. 2-1-5 (a) Switched-RC N-path filter. (b) Single port, single ended N-path filter. (c) Multiphase clocking. (d) Typical input and output signal [117]

Based on the above analysis, N-path filter has some very attractive features, which make it a good choice in wireless transceivers. It can achieve very good frequency selectivity by simply increasing the sharpness of the low-pass filter. Its center frequency is easy to be tuned by changing the switching frequency and it is easy to be fully integrated as no inductor is needed.

Although most frequencies different from switching frequency can be filtered out by N-path filter, the input signals around the harmonics of switching frequency can't be eliminated by the configuration in Fig. 2-1-5. To cancel the even harmonics, we can apply the differential structure as shown in Fig. 2-1-6(a).

With this architecture, for input signals around the even harmonics of the switching frequency, no net charge is stored on the capacitor in the steady state and no up-converted signal appears at the output node. To investigate other characteristics of the frequency response of the N-path filter in order to guide the design [29, 34-53], the complete output spectrum of differential N-path filter can be given by (2-1-1) to (2-1-4) [117]-[119].

$$V_{out}(f) = \sum_{n=-\infty}^{\infty} H_n(f) V_{in}(f - nf_S), \qquad (2-1-1)$$

$$H_n(f) = \sum_{m=0}^{N-1} exp(-j2\pi n\sigma_m f_S) H_{n,m}(f), \qquad (2-1-2)$$

$$H_{n,m}(f) = \frac{1}{1 + \frac{jf}{f_{rc}}} \left( \left( \frac{1 - exp(-j2\pi n\tau_m f_S)}{j2\pi n} \right) + \frac{1 + exp(-j2\pi \tau_{m+1}(f - nf_S) - j2\pi n\tau_m f_S)}{\frac{2\pi f_{rc}}{f_S}} G_{0,m}(f) \right),$$

(2-1-3)

$$G_{0,m}(f) = -\frac{exp(j2\pi\tau_m(f-nf_S)) - exp(-2\pi\tau_m f_{rc})}{exp(\frac{j\pi(f-nf_S)}{f_S}) + exp(-2\pi\tau_m f_{rc})} \frac{1}{1 + \frac{j(f-nf_S)}{f_{rc}}},$$

(2-1-4)

where  $f_{rc} = (\pi RC)^{-1}$ , which is the 3-dB bandwidth of a single low-pass filter composed of resistor R/2 and capacitor C (as shown in Fig. 2-1-6(b)). Also, according to Fig. 2-1-6(b),  $\tau_{m+1} = T_s/2 - \tau_m$  for each path and  $\sigma_m = \sum_{n=0}^{m-1} \tau_n$ .

Fig. 2-1-6 (a) Single port differential 4-path filter (b) Kernel model for (a)

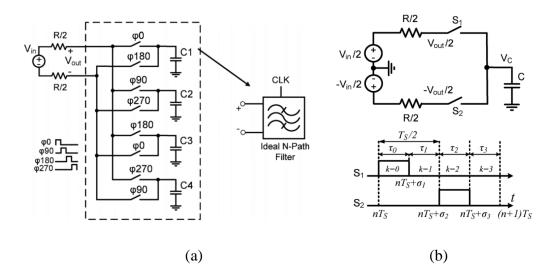

$H_0(f)$  is the desired filtering characteristic without any translation. However, according to (2-1-3), it's not defined, and we can only derive its expression by taking the limit of  $H_n(f)$  when *n* approaches continuously to zero. Moreover, in (2-1-3), we assume that the switches for different branches are on continuously, i.e.  $\tau_0 = \tau_1 = \cdots = \tau_{n-1} = DT_s$ .

Fig. 2-1-7(a) shows the theoretical and simulated curves of  $H_0(f)$  in the case where N = 4, D = 1/4,  $R = 100\Omega$ , C = 50pF and  $f_s = 500$ MHz and it's clear that the expression can

reflect its characteristic very well. Thanks to the differential architecture, peaking around even harmonics does not occur, however, there are still response peaks around odd harmonics of the switching frequency.

Fig. 2-1-7 (a) Theoretical and simulated curve for  $H_0(f)$  (b)  $H_n(f)$  around the switching frequency for a 4-path filter

Now we consider  $H_n(f)$  for  $n \neq 0$ , according to (2-1-2),  $H_n(f)$  equals to 0 except the cases when  $n = 0, \pm 1, \pm 2, \cdots$  Fig. 2-1-7(b) shows the curves for  $H_n(f)$  around the switching frequency with different values of n.

As can be seen from Fig. 2-1-7(b) and taking (2-1-1) into consideration, input frequencies around  $k(N\pm 1)f_s$  will "fold back" to the desired band around  $f_s$ . In general, increasing the number of paths will increase the distance between  $f_s$  and the first folded component around  $(N-1)f_s$ .

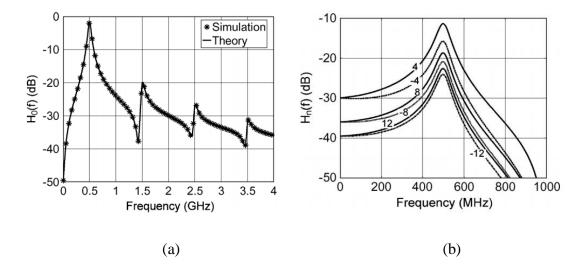

For N-path filter, at any moment there are two switches in the on-state and their noise contributions are not correlated. Thus, we can use the model in Fig. 2-1-8 to analysis the noise voltage.

For Fig. 2-1-8(a), we can find the expression of the thermal noise due to *R*:

$$N_{out,R}(f) = \left|\frac{2R_{SW} + RH_0(f)}{R + 2R_{SW}}\right|^2 N_R(f) + \sum_{n = -\infty, n \neq 0}^{\infty} \left|\frac{R}{R + 2R_{SW}} H_n(f)\right|^2 N_R(f - nf_S).$$

(2-1-5)

The first term accounts for the noise power, which appears at the output without any frequency translation, and the second part accounts for noise folding, where  $N_R(f-nf_s)$  is the frequency-shifted version of the noise power generated by R.

For the circuit in Fig. 2-1-8(b), we can similarly derive the output noise power due to switch resistance:

$$N_{out,SW}(f) = \left(\frac{R}{R+2R_{SW}}\right)^2 \left(|H_0(f) - 1|^2 N_{SW}(f) + \sum_{n=-\infty, n\neq 0}^{\infty} |H_n(f)|^2 N_{SW}(f - nf_S)\right).$$

(2-1-6)

Fig. 2-1-8 The model for noise calculation. (a) Source noise (b) Switch resistance noise

Again, the first part of (2-1-6) corresponds to the noise power without frequency translation. Since  $H_0(f)$  is close to 1 around the switching frequency for an N-path filter, the contribution of the first part is very small. The second part is the noise folding term and turns out to be almost negligible. Finally, the noise factor can be calculated by  $F = N_{out}/(A_v^2 N_{in})$  and is mainly determined by the noise coming from the source resistance *R*.

Fig. 2-1-9 (a) Wideband RX with an off-chip RF bandpass filter (b) Wideband RX front end with an N-path filter at the RF input (c) mixer-first RX front end (d) Switched capacitor RX front end

Fig. 2-1-9 gives several different ways to apply N-path filter in the wireless receiver design. In Fig. 2-1-9 (b), an N-path filter is located before the LNA, which can attenuate

RF input blockers, but the stop-band rejection is limited by the switch-on resistance due to the single-port architecture of the filter [120][121]. In mixer-first RXs as shown in Fig. 2-1-9 (c), the stop-band rejection is no longer an issue because the active amplifiers are attached to capacitors. But the bandwidth of the baseband (BB) amplifier may need to be large, which leads to high power consumption [122]-[126]. In Fig. 2-1-9 (d), the authors in [127] proposed a switch capacitor front end where the high-order filtering is achieved by linear passive switch capacitor (SC) circuits.

Another example of the N-path filter based receiver is [128]. The overall structure is depicted in Fig. 2-1-10(a), noting that this is a single-ended version. The front end is composed of eight RF SC branches, baseband  $G_m$  cells and trans-impedance amplifiers. All the switches are driven by an eight-phase, non-overlapping clock signal p<i> as shown in Fig. 2-1-10(b), noting that *i* is an integer from 0 to 7. The clock frequency is  $f_s$ , and because there are eight non-overlapping phases, the equivalent local oscillator (LO) frequency is  $f_{io}=f_s/8$ . At the RF input, an 8-path band-pass filter is realized by the capacitors  $C_{ho}<i>$  and the switches  $s_0<i>$  in all the eight branches. The N-path first structure can attenuate the out-of-band blockers effectively. After that, impedance matching is realized by capacitors  $C_s<i>$ , switches  $s_1<i>$  and switches  $s_6<i>$ . Also in this stage, the RF signal is sampled on  $C_s<i>$ , and a discrete-time signal is obtained. After sampling, history capacitors  $C_{h1}<i>-C_{h3}<i>$  and the switches attached to those capacitors ( $s_2<i>-s_4<i>$ ) together with  $C_s<i>$  form another high-order discrete-time infinite-impulse-response filter and the output of this filter is provided to the baseband G<sub>m</sub> cells. The G<sub>m</sub> cells down-converters the filtered signal and the TIA outputs the signal after proper amplification.

Fig. 2-1-10 (a) Simplified architecture of a single-ended SC RF front end (b) Clock waveform (c) Operation of the SC RF front end [128]

As discussed before, such SC front end achieves different circuit functions according to the on-off status of the switches, and Fig. 2-1-10 (c) shows the function sequences. Taking the first branch as an example, the RF signal is sampled on Cs in sampling phase  $p_1$ , propagated to the G<sub>m</sub> input node in  $p_5$ , and zeroed to ground in  $p_7$ . From 31

$p_2$  to  $p_4$ , the signal is filtered with increasing order. The blank time intervals relax the timing constraints, and the eight banks operate in a time-interleaved manner.

The authors in [128] successfully prove that SC circuits can be applied in the generic RF receiver structure. And this further motivates us to apply the N-path filter in FSK demodulator for IoT wireless sensors to achieve a low power frequency tunable receiver as given in Chapter 3. Table 2-1-1 summarizes the performance for state-of-the-art low power FSK receiver publications, and we can see that the tunability is a common issue. Other than that, our design also aims to maintain a good sensitivity and energy per bit.

| Reference              | [93]    | [96]  | [97]    | [98]  | [101]  | [102] |

|------------------------|---------|-------|---------|-------|--------|-------|

| Technology(µm)         | 0.13    | 0.18  | 0.18    | 0.065 | 0.04   | 0.18  |

| Supply(V)              | 1.2     | 1     | 0.45    | 0.75  | 0.95   | 0.7   |

| Modulation             | FSK     | FSK   | FSK     | GFSK  | FSK    | FSK   |

| Sensitivity(dBm)       | -78     | -78   | -69     | -58   | -90    | -62   |

| Frequency(MHz)         | 902-908 | 433   | 402-405 | 2400  | 5800   | 72-80 |

| Tunability             | No      | No    | No      | No    | No     | No    |

| Data Rate(Mbps)        | 8       | 0.2   | 0.12    | 1     | 0.0625 | 0.312 |

| Power                  | 639     | 54    | 352     | 164   | 490    | 45    |

| Consumption(µW)        |         |       |         |       |        |       |

| Energy per bit(nJ/bit) | 0.08    | 0.055 | 1       | 0.164 | 7.8    | 0.14  |

Table 2-1-1 Performance summary of state-of-the-art FSK receiver

#### 2.1.2 Low-Power Frequency Synthesizers

A frequency synthesizer can generate a range of accurate frequencies from a single reference frequency, and the ratio between them can be either integer or fractional number. There are several different techniques for the design of frequency synthesizer, such as

direct digital synthesis, frequency multiplication, frequency division, frequency mixing and PLL. Currently, the PLL-based frequency synthesizer is the most commonly used structure and there are many researchers focusing on this area. Fig. 2-1-11 shows the basic structure of the PLL-based frequency synthesizer [129].

Fig. 2-1-11 Structure of a PLL-based frequency synthesizer

The core of the frequency synthesizer shown in Fig. 2-1-11 is the phase comparator. It compares the phases of two input signals and produces an error signal that is proportional to the difference between their phases. The error signal is then low pass filtered and used to drive a voltage-controlled oscillator (VCO) which creates an output frequency. The output frequency is fed through a frequency divider back to the input of the system, producing a negative feedback loop. If the output frequency drifts, the phase error signal will increase, driving the frequency in the opposite direction in order to reduce the error. Thus, the output is locked to the frequency at the other input. This other input is called the reference and is usually derived from a crystal oscillator, which is very stable in frequency.

In practice this type of frequency synthesizer cannot operate over a very wide range of frequencies, because the comparator will have a limited bandwidth and may suffer from aliasing problems. This would lead to false locking situations, or an inability to lock at all. In addition to the locking range problem, power consumption is another major concern for the design of frequency synthesizer. There are many attempts trying to solve these issues [130]-[134].

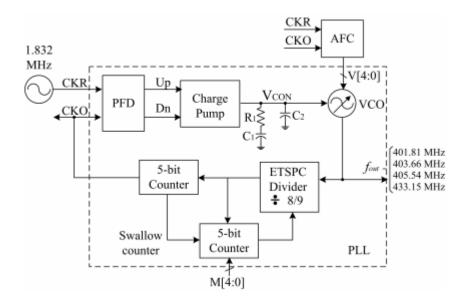

In [131], the authors proposed a 0.5 V, 440  $\mu$ W frequency synthesizer and its architecture is shown in Fig. 2-1-12.

Fig. 2-1-12 Architecture of a 0.5V, 440µW frequency synthesizer [131]

The frequency synthesizer is composed of a dynamic phase-frequency detector (PFD), a charge pump (CP) with low static power and high output current, a low-power ring-based VCO, a frequency divider, an external second-order low-pass filter (LPF) and an automatic frequency calibration (AFC) circuit which is used to compensate the process, voltage and temperature (PVT) variations of the VCO. Due to the limited voltage headroom with 0.5V voltage supply, the nominal threshold voltage transistors or even the low-V<sub>th</sub> transistors are hard to apply. Thus, the authors adopt dynamic threshold CMOS (DTCMOS) transistors to reduce the  $V_{th}$  while maintaining low leakage current. For such transistors, the gate and the body are connected, so the forward body bias voltage can greatly reduce the threshold voltage when the transistors are on. Once the transistors are off, V<sub>th</sub> returns to its nominal value and the leakage current is limited.

Fig. 2-1-13 Schematic of the VCO in [131]

Fig. 2-1-13 shows the schematic of the VCO, which is a differential ring-based VCO with dual resistor-varactor tuning. The varactors in each delay cell are controlled by the analog signal ( $V_{\text{CON}}$ ) generated from charge pump to fine-tune the frequency generated by the VCO, while an NMOS current biasing array is digitally controlled by 5-bit word to compensate PVT effects.

As the low power design for PLL based frequency synthesizer may require many peripheral and off-chip calibrations, injection locking technique is more and more popular now for frequency synthesizer design. The phenomenon of injection locking happens when a free running harmonic oscillator is disturbed by another oscillator with a close enough frequency. If the coupling from the second oscillator is strong enough, the first oscillator will be forced to operate in the same frequency as the second one [135][136]. Based on this principle, injection-locked oscillator (ILO) can be used to obtain a desired frequency and it is also called injection-locked clock multiplier (ILCM) [137]-[141].

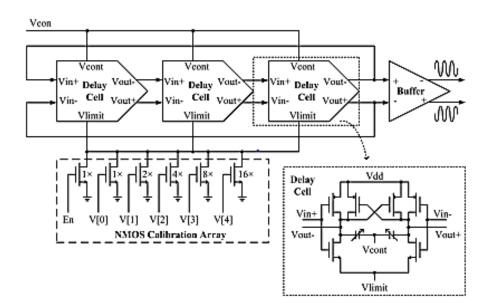

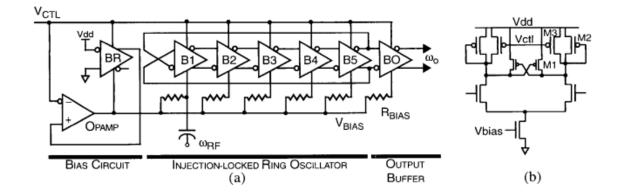

Fig. 2-1-14 Schematic of the (a) 5-stage ring oscillator and (b) differential delay buffer in [139]

In [139], the authors exploited injection-locking in different CMOS ring oscillators as shown in Fig. 2-1-14. The center frequency can be tuned by changing the biasing of the buffers so as the delay through each cell. The delay buffer has a structure of cross-coupled symmetric load as shown in Fig. 2-1-14(b), which has good supply noise rejection and low 1/*f* noise up-conversion characteristics. The RF signal is injected at the tail current source of the first buffer, and the rest of the buffer stages behave as filters to contribute the gain and phase shift required to sustain the oscillation.

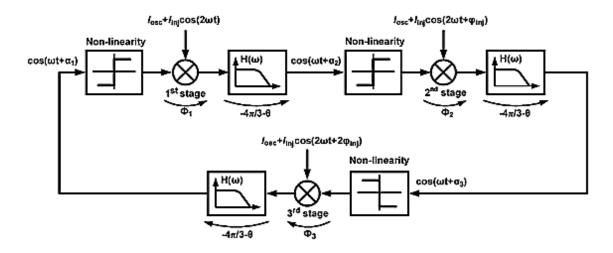

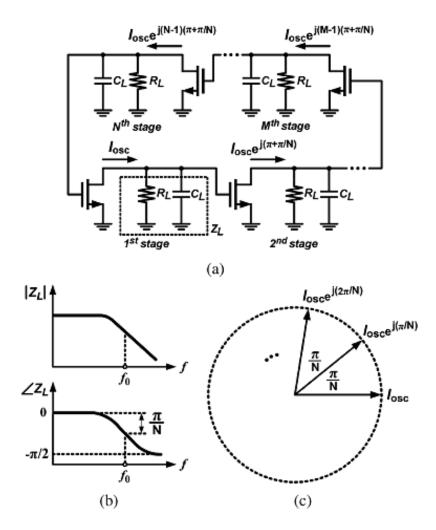

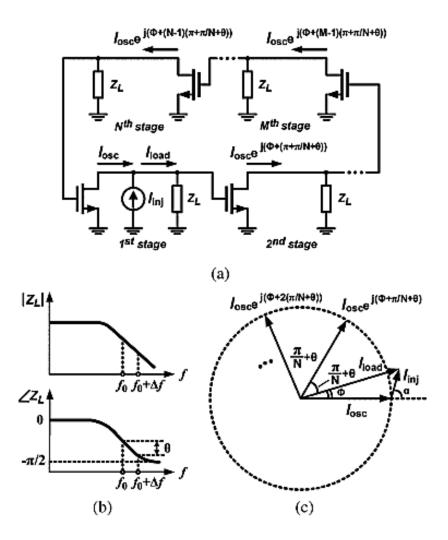

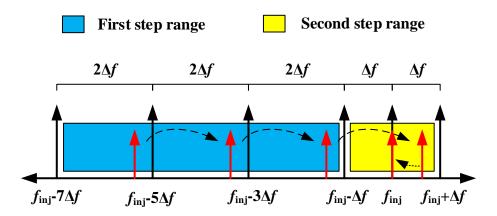

Although single-injection oscillator has been proved to be able to provide accurate oscillation frequency, its locking range (LR) is limited. To widen the LR, the idea of multiple injections comes up by injecting multiple properly phase shifted signals into the multiple nodes of the ring oscillator [142]-[147]. It's shown in [xx] that the LR can be widened by a sequence of injection phases which progress with the intrinsic phase delay of a single stage of the oscillator.