## A HIGHLY-SCALABLE DC-COUPLED DIRECT-ADC NEURAL RECORDING CHANNEL ARCHITECTURE WITH INPUT-ADAPTIVE RESOLUTION

SAYEDEH MINA SAYEDI

#### A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

#### GRADUATE PROGRAMME IN COMPUTER SCIENCE YORK UNIVERSITY TORONTO, ONTARIO

SEPTEMBER 2022

© SAYEDEH MINA SAYEDI 2022

### ABSTRACT

This thesis presents the design, development, and characterization of a novel neural recording channel architecture with (a) quantization resolution that is adaptive to the input signal's level of activity, (b) fully-dynamic power consumption that is linearly proportional to the recording resolution, and (c) immunity to DC offset and drifts as well as artifacts at the input. Our results demonstrate the proposed design's capability in conducting neural recording with near lossless input-adaptive data compression, leading to a significant reduction in the energy required for both recording and data transmission, hence allowing for a potential high scaling of the number of recording channels integrated on a single implanted microchip without the need to increase the power budget.

The proposed design adopts a neural ADC with a novel integrating-summing feedback DAC that removes the need for area-intensive multi-bit capacitive/resistive DACs reported in state of the art, leading to a substantial reduction in the required silicon area for each channel, and more importantly, very promising design scalability with CMOS technology nodes. The proposed neural recording channel architecture is capable of removing input DC offsets and drifts as well as all other low-frequency undesired interferences such as motion/stimulation artifacts. The proposed channel with the implemented compression technique is implemented in a standard 130nm CMOS technology with overall power consumption of 7.6uW and active area of 92×92µm for the implemented digital-backend.

### ACKNOWLEDGMNET

First and foremost, I would like to sincerely thank my supervisor Dr. Hossein Kassiri. About two years of continuous work with Dr. Kassiri was a great and rewarding experience. I gained great insights into this field through him. He patiently directed my research and enlightened me with valuable advice and guidance to make this work possible.

I would like to express my gratitude to my committee members, Dr. Amir Sodagar, Dr. Regina Lee and Dr. Amirali Amirsoleimani for their great feedback and valuable comments on this thesis.

I would like to thank my colleagues Mahdi Nekoui and Tayebeh Yousefi who patiently shared their experience and knowledge of CAD tools with me and making this research possible.

I would also like to thank my colleagues and ICSL members, Alireza Dabbaghian, Tania Moeinfard, Mansour Taghadosi and Parsa Farshatfar for making my master's studies a memorable experience.

Finally, I want to express my deepest gratitude to my parents and my family members Sara and Mehran for always providing me with continuous encouragement and motivation throughout the years and through the process of researching and writing this thesis.

## TABLE OF CONTENTS

| ABSTRACT                                          | .ii  |

|---------------------------------------------------|------|

| ACKNOWLEDGMNET                                    | iii  |

| TABLE OF CONTENTS                                 | iv   |

| LIST OF TABLES                                    | /iii |

| LIST OF FIGURES                                   | vii  |

| LIST OF ACRONYMS                                  | xi   |

| Chapter 1 Introduction and Motivation             | . 1  |

| 1.1 Motivation and objectives                     | . 1  |

| 1.1.1 Implantable BMIs                            | . 3  |

| 1.1.2 Power constraints for channel count scaling | 4    |

| 1.2 Data Compression                              | . 6  |

| 1.2.1 Introduction and trade-offs                 | . 6  |

| 1.2.2 Information sparsity                        | . 8  |

| 1.2.3 Compressive sensing                         | . 8  |

| 1.2.4 Adaptive sampling                           | 10   |

| 1.3 Adaptive resolution                           | 12   |

| 1.4 The | esis Organization                               | 14 |

|---------|-------------------------------------------------|----|

| Chapter | 2 System-Level Implementation                   | 15 |

| 2.1 E   | Background Theory                               | 16 |

| 2.1.1   | Events in Neural Recording                      | 16 |

| 2.1.2   | Neural ADCs                                     | 17 |

| 2.1.3   | Adaptive Resolution vs. Adaptive Sampling       | 19 |

| 2.2 F   | Functional Implementation                       | 23 |

| 2.2.1   | Digital Back-End                                | 23 |

| 2.2.2   | Mixed-Signal Front-End                          | 27 |

| 2.3 N   | MATLAB Simulation Results                       | 32 |

| Chapter | 3 Digital Back-End On-Chip Implementation       | 39 |

| 3.1 E   | Block-level Implementation                      | 40 |

| 3.1.1   | Decimation filter                               | 41 |

| 3.1.2   | Activity detection unit                         | 42 |

| 3.1.3   | Baseline calculator unit                        | 47 |

| 3.1.4   | Clock generator and selector unit               | 49 |

| 3.2 0   | Overall Back-end Integration and Implementation | 50 |

| 3.3 F   | Physical Layout                                 | 54 |

| 3.3.1   | Power overhead of Digital Back-end              | 55 |

| 3.4 0   | Chip Fabrication and Measurement Setup          | 56 |

| Chapter 4 Mixed-Signal Front-End Implementation                          | 58 |

|--------------------------------------------------------------------------|----|

| 4.1 Digital-to-analog converter (DAC)                                    | 60 |

| 4.2 Integrator circuit ( <i>Gm</i> -C stage)                             | 67 |

| 4.3 Voltage comparator                                                   | 74 |

| 4.4 Simulation results                                                   | 75 |

| Chapter 5 Conclusions and Future Directions                              | 81 |

| 5.1 Conclusion                                                           | 81 |

| 5.2 Statement on contributions                                           | 83 |

| 5.3 Future work                                                          | 83 |

| 5.3.1 Improvement of the non-ideal effects on the front-end              | 84 |

| 5.3.2 Improvement on the signal transient recovery                       | 84 |

| 5.3.3 Low power transmitter and data packaging                           | 85 |

| 5.3.4 Multi-channel implementation                                       | 85 |

| Appendix A                                                               | 86 |

| A.1. MATLAB code of the described system                                 | 86 |

| A.2. Verilog code for FPGA board to generate inputs for chip measurement | 96 |

| A.3. Description of the measurement setup 1                              | 01 |

| Bibliography 1                                                           | 03 |

## LIST OF TABLES

| Table 1.1 Power breakdown of implantable BMIs illustrating the Tx's significant share of the    |

|-------------------------------------------------------------------------------------------------|

| total power consumption                                                                         |

| Table 1.2 Tx power consumption of implantable BMIs in various works       6                     |

| Table 2.1 $\Delta w$ for the four possible outcomes based on v[n] and its previous value v[n-1] |

| Table 2.2 Statistical summary of the simulation results presented in Figure 2.11.       36      |

| Table 2.3 Statistical summary of the simulation results presented in Figure 2.12.    37         |

| Table 3.1 Digital back-end input values    51                                                   |

| Table 3.2 Digital back-end's specifications                                                     |

| Table 4.1 Specifications of the neural front-end                                                |

| Table 4.2 Size and bias points of the DAC's OTA                                                 |

| Table 4.3 Size and bias points of Gm stage amplifier                                            |

| Table 4.4 Size and bias points of the CF amplifier                                              |

| Table 4.5 performance parameter of the Gm – C stage                                             |

| Table 4.6 Performance comparison with the state of the art                                      |

## LIST OF FIGURES

| Figure 1.1 Comparison between temporal resolution vs. spatial resolution and coverage of         |

|--------------------------------------------------------------------------------------------------|

| several brain monitoring techniques [10]                                                         |

| Figure 1.2 Top-level block diagram of a typical wireless BMI and its envisioned interfacing with |

| the brain cortex                                                                                 |

| Figure 1.3 Simplified block diagram of different generic and application-specific                |

| Figure 1.4 EEG signal sparsity in wavelet domain [15]                                            |

| Figure 1.5 Block diagram of a typical CS tranmitter and reciver                                  |

| Figure 1.6 EEG signal with events periods marked as A and idle periods as B 11                   |

| Figure 1.7 Concept of adaptive sampling 12                                                       |

| Figure 1.8 An example of missing short high-activity periods in adaptive sampling 12             |

| Figure 1.9 Conceptual difference between adaptive sampling and adaptive resolution techniques    |

|                                                                                                  |

| Figure 2.1 An example of (a) high-activity event (b) noise interferences that unwantedly are     |

| detected as a high-activity event[39]16                                                          |

| Figure 2.2 (a) conventional and (b) direct-ADC recording front-end concepts                      |

| Figure 2.3 Comparison between adaptive sampling and adaptive resolution techniques               |

| Figure 2.4 Internal block diagram of the digital backend blocks of the proposed adaptive-        |

| resolution neural ADC                                                                            |

| Figure 2.5 Output of the N-bit U/D counter; counter is designed for the high resolution; the lower |

|----------------------------------------------------------------------------------------------------|

| resolution is achieved by increasing the UP/DOWN counting step size                                |

| Figure 2.6 system-level diagram of the proposed $\Delta$ - $\Delta\Sigma$ front-end architecture   |

| Figure 2.7 Block diagram of the proposed $\Delta$ - $\Delta\Sigma$ ADC                             |

| Figure 2.8 w results for random output bit sequence ( for w calculation bit 0 is equivalent to -1) |

|                                                                                                    |

| Figure 2.9 Frequency response of the proposed mixed signal front-end in MATLAB, for 4-bit          |

| and 8-bit resolution from left to right                                                            |

| Figure 2.10 EEG signal (top), the reconstructed output with adaptive resolutions (middle), and     |

| the automatically calculated baseline (bottom)                                                     |

| Figure 2.11 An example of system's response to an EEG signal with seizure                          |

| Figure 2.12 An example of the proposed system's response to an EEG signal containing a seizure     |

| episode                                                                                            |

| Figure 3.1 Top-level block diagram of the proposed recording channel and the detailed              |

| implementation of the digital blocks 40                                                            |

| Figure 3.2 Logic of decimation filter                                                              |

| Figure 3.3 Threshold levels and "CLOCK SLECTOR" flag value versus signal magnitude                 |

| variations                                                                                         |

| Figure 3.4 Simplified RTL implementation of the activity detection unit: (a) Setting mid-range     |

| threshold levels and signal position with respect to the high/low thresholds (b) determining the   |

| new value of flag "FLAG_LOW_BAND" and "FLAG_HIGH_BAND" (c) determining                             |

| "CLOCK SELECTOR" value                                                                             |

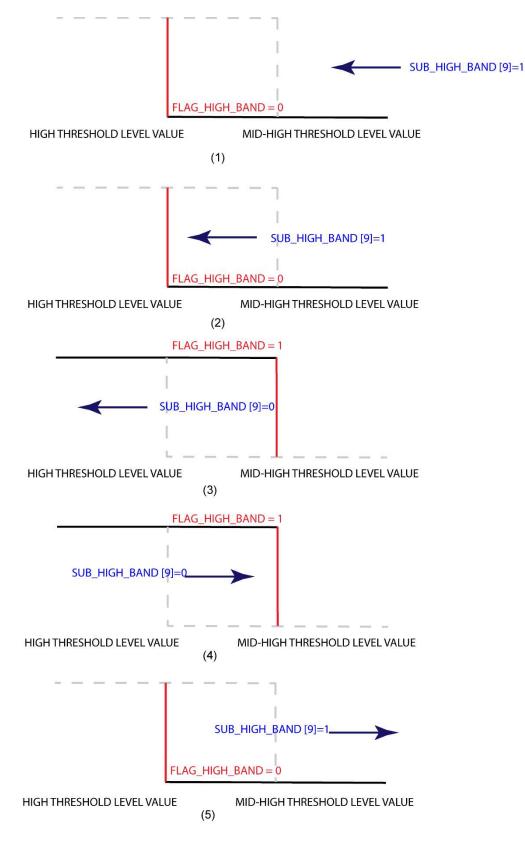

| Figure 3.5 Flags behavior for the activity detection unit with respect to threshold levels, figure      |

|---------------------------------------------------------------------------------------------------------|

| only depicts for high threshold levels, same behavior for low threshold levels                          |

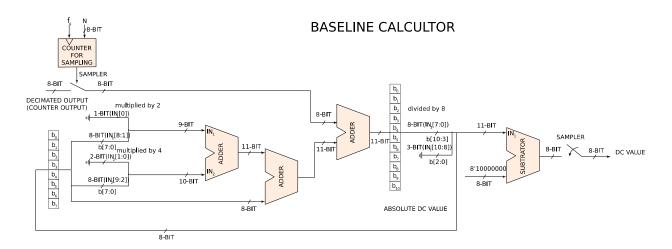

| Figure 3.6 Internal block diagram of the baseline calculator unit                                       |

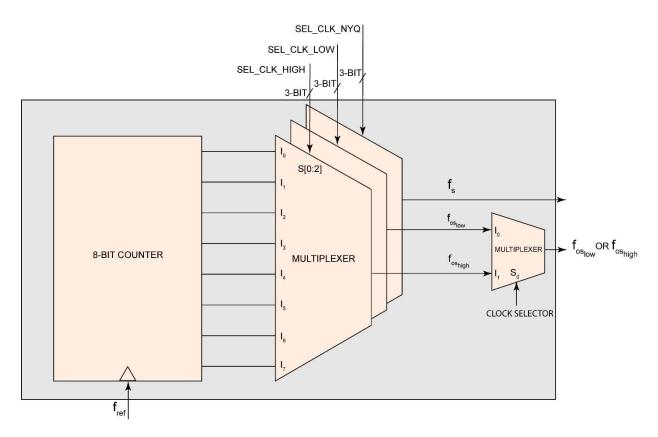

| Figure 3.7 Logic of clock generator & selector unit                                                     |

| Figure 3.8 Overall block diagram of system 50                                                           |

| Figure 3.9 Simulation results for clock generator unit                                                  |

| Figure 3.10 Simulation results for activity detection and decimation filter unit                        |

| Figure 3.11 Simulation results for baseline calculator unit                                             |

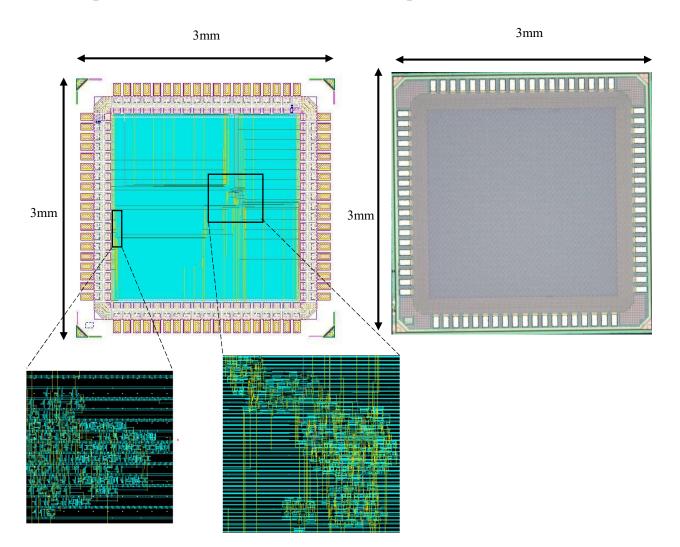

| Figure 3.12 Chip's layout and the micrograph                                                            |

| Figure 3.13 Lab set up for chip's measurement test                                                      |

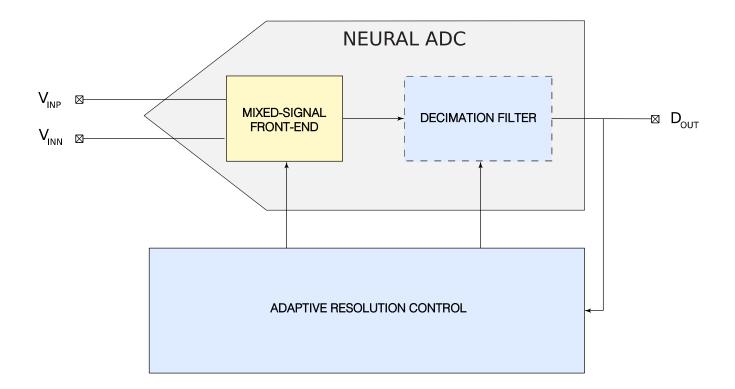

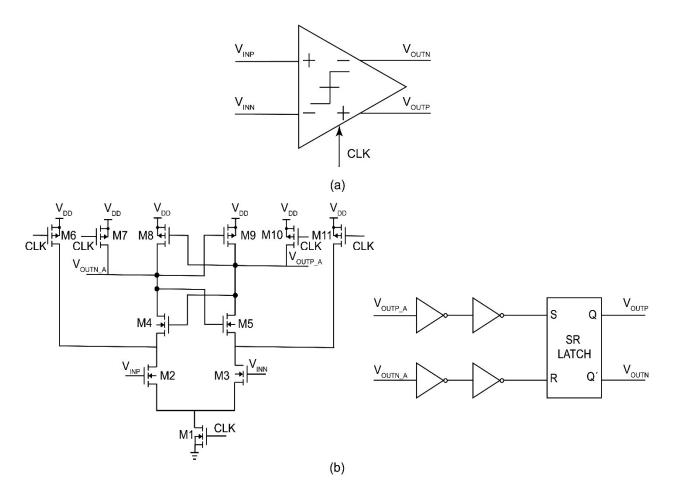

| Figure 4.1 Top level block diagram of the presented recording channel 59                                |

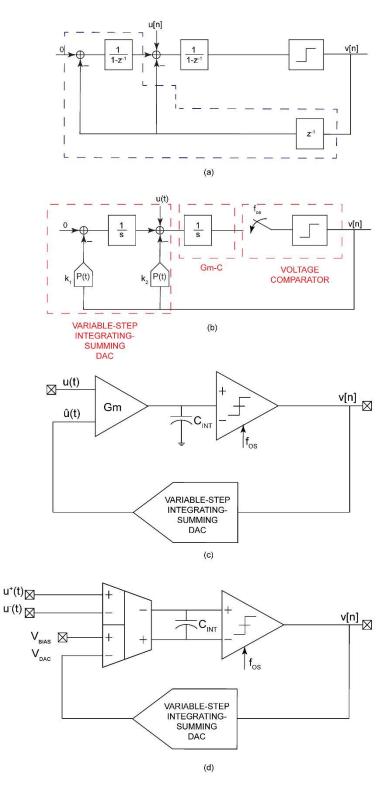

| Figure 4.2 (a) Discrete time (DT) and (b) continuous-time (CT) 2nd order $\Delta\Sigma$ modulator block |

| diagram with input arrangements that result in second-order noise shaping and first-order signal        |

| shaping (i.e., $\Delta$ modulation). Proposed mixed-signal front-end architecture                       |

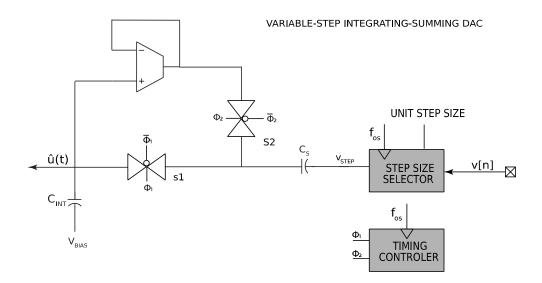

| Figure 4.3 Internal architecture of the variable-step integrating-summing DAC                           |

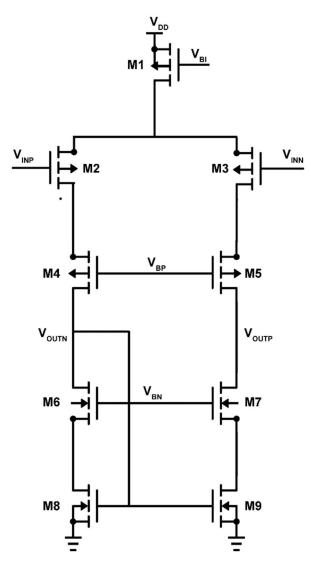

| Figure 4.4 Telescopic OTA used in the DAC circuit                                                       |

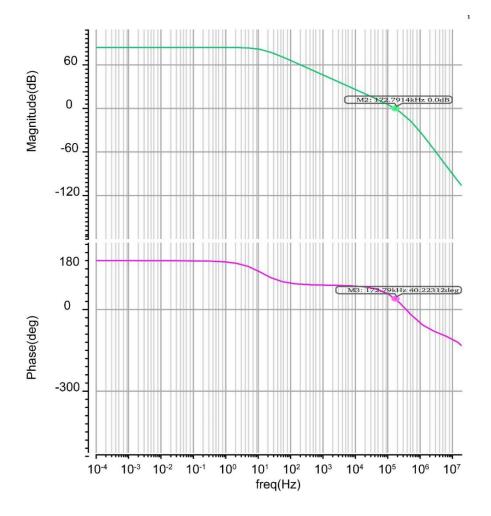

| Figure 4.5 Frequency response of the designed OTA                                                       |

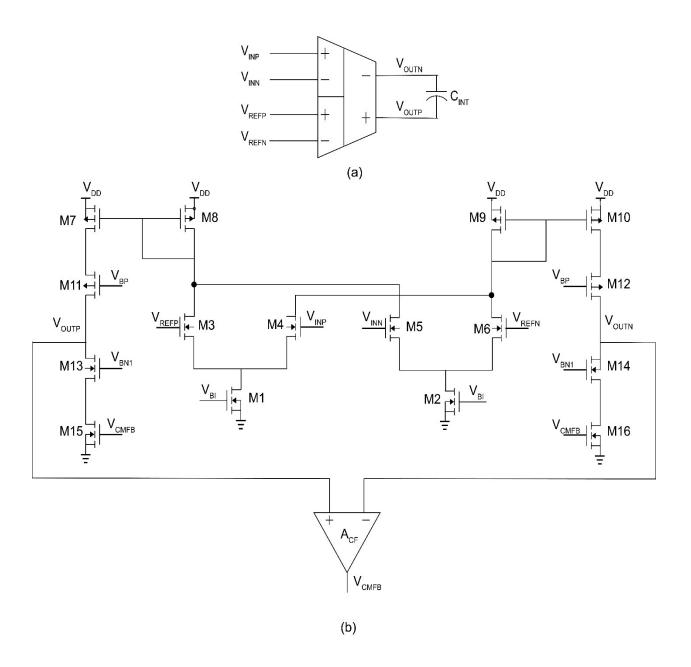

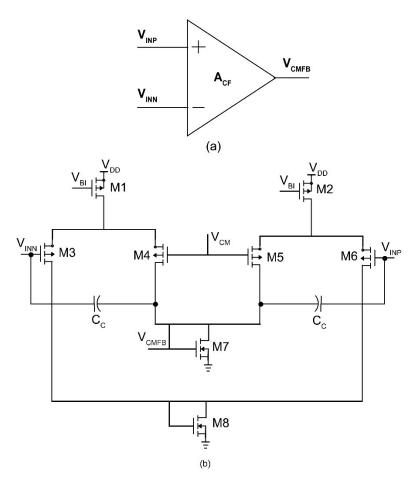

| Figure 4.6 Detailed schematic of the Gm-C circuit                                                       |

| Figure 4.7 Detailed schematic of the (CMFB) circuit that is shown as; A_CF in the Gm-C circuit.         |

|                                                                                                         |

| Figure 4.8 Frequency response of the designed G_m-C stage                                               |

| Figure 4.9 Power spectral density of the IRN of the designed Gm – C stage                               |

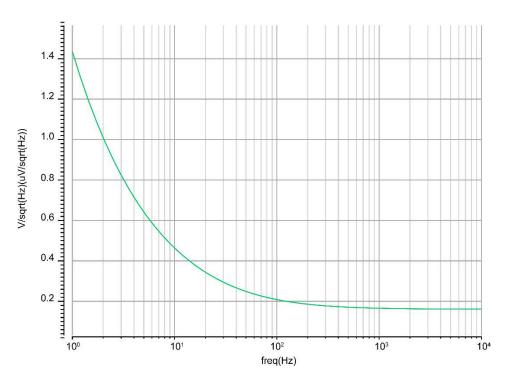

| Figure 4.10 Transistor-level schematic of the StrongArm voltage comparator used in the       |

|----------------------------------------------------------------------------------------------|

| proposed mixed-signal front-end74                                                            |

| Figure 4.11 Block diagram of the $\Delta\Sigma$ modulator                                    |

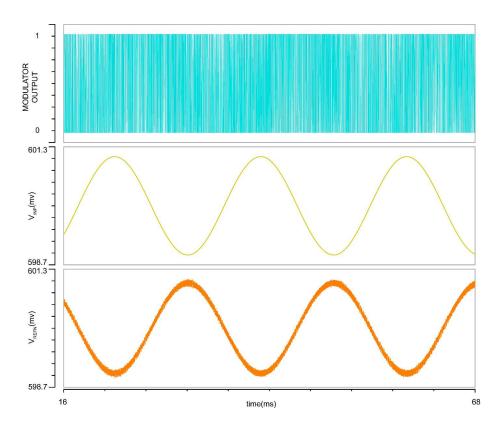

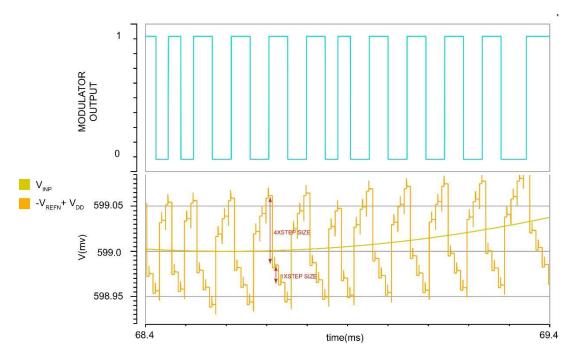

| Figure 4.12 VREFN delayed version of the input (VINP) made from the Modulator's output using |

| the proposed DAC76                                                                           |

| Figure 4.13 Step size integration according to modulators output bit stream sequence77       |

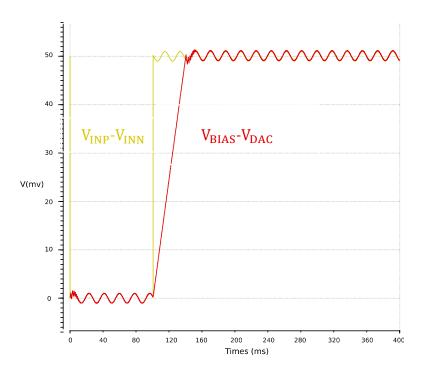

| Figure 4.14 Input DC drift cancelation through the proposed DAC architecture                 |

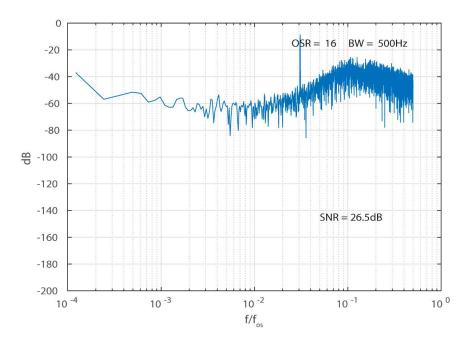

| Figure 4.15 FFT of the modulator's output for OSR=16 (4-bit resolution)                      |

| Figure 4.16 FFT of the modulator's output for OSR=64 (8-bit resolution)                      |

## LIST OF ACRONYMS

| Acronym | Meaning                                                           |  |  |  |  |

|---------|-------------------------------------------------------------------|--|--|--|--|

| MEG     | Magnetoencephalography                                            |  |  |  |  |

| РЕТ     | Positron Emission Tomography                                      |  |  |  |  |

| MRI     | Magnetic Resonance Imaging                                        |  |  |  |  |

| iEEG    | Intracranial EEG                                                  |  |  |  |  |

| EEG     | Electroencephalography                                            |  |  |  |  |

| ECoG    | Electrocorticography                                              |  |  |  |  |

| ECG     | Electrocardiogram                                                 |  |  |  |  |

| EMG     | Electromyography                                                  |  |  |  |  |

| DAC     | Digital-to-Analog Converter                                       |  |  |  |  |

| ADC     | Analog-to-Digital Converter                                       |  |  |  |  |

| CMRR    | Common Mode Rejection Ratio                                       |  |  |  |  |

| IRN     | Input Referred Noise                                              |  |  |  |  |

| SAR ADC | Successive-Approximation-Register Analog-<br>to-Digital Converter |  |  |  |  |

| СТ      | Continuous time                                                   |  |  |  |  |

| DT      | Discrete time                                                     |  |  |  |  |

# Chapter 1 Introduction and Motivation

#### 1.1 Motivation and objectives

Neurological disorders affect more than one billion people worldwide today, and the number is expected to increase with the world's aging population [1]. Accurate detection and effective control of these disorders require continuous monitoring of brain neuronal activities with high spatial and temporal resolution. Over the past decade, thanks to the advancements in the fields of neurotechnology and microelectronics, various implantable and wearable brain machine interfaces (BMI) have been developed to monitor, diagnose, and control different neurological disorders [2-9,47-50].

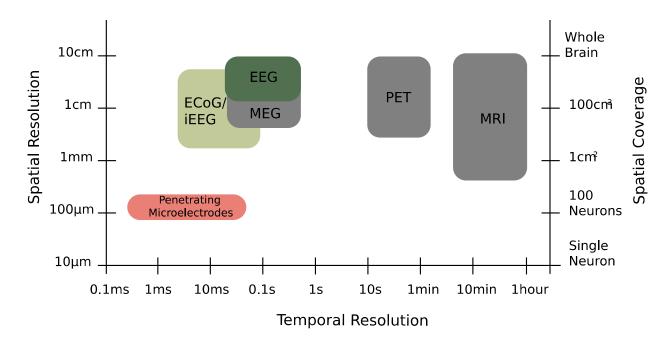

Figure 1.1 Comparison between temporal resolution vs. spatial resolution and coverage of several brain monitoring techniques [10]

In Figure 1.1, various methods for brain activity monitoring is shown. Each of them come at its own advantage and disadvantages. Methods such as magnetoencephalography (MEG), positron emission tomography (PET), magnetic resonance imaging (MRI), while are noninvasive, are not suitable for ambulatory applications due to either of size constraints, portability, power requirements, and poor temporal resolution [10]. Highly-invasive methods such as intracranial EEG (iEEG) using penetrating microelectrodes offer not only high spatial resolution, which is necessary for capturing time-sensitive neurological events (e.g., epilepsy seizures [51]), but also high temporal resolution (i.e., update rate). However, this type of monitoring can cause substantial damage to the brain tissues, thus is only used in severe conditions when all other options are exhausted. On the other hand, less-invasive electrophysiological recording methods such as scalp (or surface) electroencephalography (EEG) [52][53], and electro-corticography (ECoG) allow for monitoring with high temporal resolution. Depending on the application and the required spatial

resolution and spatial coverage, one of these technologies are used for long-term monitoring of the patient's neural activity [10].

#### 1.1.1 Implantable BMIs

Timely and accurate detection of neurological events often requires long term (i.e., months to years) monitoring of brain activity from a widespread network of neurons on the brain. For these situations, a feasible solution is to develop wireless cm-scale BMI devices implanted under the scalp (to be minimally obtrusive for the patient) and connected to an ECoG electrode array with as many recording sites as needed to yield the desired spatial resolution and coverage. Regardless of using a battery or a wireless powering link, the energy budget of these devices is highly constrained either due to physical size limitations for the battery, or the safety limitations for power consumption and power transfer density [54]. For power transfer, the upper limit on the magnetic field intensity is set by the regulations and guidelines on the specific absorption rate (SAR) [11]. Based on these guidelines, the total heat density created by the magnetic field anywhere in the body cannot exceed the rate of 1.6W/Kg [11]. Additionally, heat dissipation within an implantable BMI resulting in one-degree Celsius temperature increase is deemed unsafe for the cortex tissue. This corresponds to an overall system power density of 15-80mW/cm2 [12], depending on the heat conductivity of the encapsulation materials.

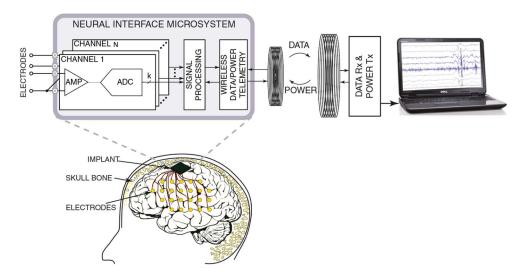

Figure 1.2 depicts the top-level block diagram of a typical fully wireless implantable BMI and how it could be interfaced with the brain. As shown, a neural recording system consists of an array of recording channels (typically, 64 or more) as well as blocks for signal processing, wireless data transmission and power telemetry [55]. Each recording channel consists of a mixed-signal front end, which is responsible for low-noise amplification, and digitization of the sensed neural data.

Figure 1.2 Top-level block diagram of a typical wireless BMI and its envisioned interfacing with the brain cortex.

#### 1.1.2 Power constraints for channel count scaling

As mentioned, to improve spatial resolution and coverage, and consequently the accuracy of neurological events detection, it is desired to have as many recording channels as possible. However, besides directly increasing the required power for recording, channel count scaling also increases the throughput required for the wireless data transmitter (Tx) to communicate the recorded data outside of the body. From power budgeting perspective, the increase in the required transmission data-rate is particularly undesirable because wireless data transmission is typically responsible for 70-to-90% of the total power consumption of implantable BMIs [13][7][3][8]. Table 1.1 lists some of the implantable neural interface integrated circuits (ICs) and the share of the total power consumption allocated to data Tx.

| Ref.                                                 | JSSC'17<br>[13] | JSSC'14<br>[7] | JSSC'15<br>[8] | JSSC'16<br>[3] | TBCAS'16<br>[14] |

|------------------------------------------------------|-----------------|----------------|----------------|----------------|------------------|

| Tech.                                                | 130nm           | 180nm          | 180nm          | 130nm          | 180nm            |

| Power/Channel<br>(μW)                                | 0.63            | 57.67          | 1.62           | 9.1            | 3.2              |

| No. of<br>Recording<br>Channels                      | 64              | 8              | 16             | 64             | 16               |

| Total Power<br>Consumption<br>(Including TX)<br>(mW) | 1.07            | 2.8            | 0.25           | 2.17           | 0.25             |

| % of TX<br>Power<br>Consumption                      | ~96%            | ~83%           | ~89%           | ~73%           | ~79%             |

Table 1.1 Power breakdown of implantable BMIs illustrating the Tx's significant share of the total power consumption

This motivates for investigating system and circuit techniques to improve energy efficiency of data Tx. Various architectures and time- and frequency-domain modulation schemes have been investigated over the past decade, and energy efficiencies in the range of a few to pJ/bit have been reported, as listed in Table 1.2. It should be noted that less efficient works (i.e., higher pJ/bit) are often yield a better transmission range and fidelity for the same bit error rate. Regardless, the data Tx remains the major power consumer in implantable BMIs and a significant bottleneck for channel count scaling [56]. As such, in parallel with efforts focusing on improving energy efficiency, it is critical to investigate approaches/methods for reducing the amount of data that needs to be transmitted (i.e., the required Tx throughput) without losing recording quality or detection accuracy [57].

| Ref.                   | TCAS-II'21<br>[16] | JSSC'15<br>[17] | JSSC'14<br>[18] | JSSC'14<br>[19] | VLSI'17<br>[20] |

|------------------------|--------------------|-----------------|-----------------|-----------------|-----------------|

| Process                | 180nm              | 180nm           | 180nm           | 90nm            | 180nm           |

| ТХ                     | OOK/FSK            | OOK             | OOK/FSK         | OOK             | OOK             |

| Modulation             |                    |                 |                 |                 |                 |

| Data Rate              | 10                 | 5               | 5               | 5               | 10              |

| (Mbps)                 |                    |                 |                 |                 |                 |

| Energy/Bit<br>(pJ/bit) | 7                  | 19.6            | 38              | 172             | 171             |

Table 1.2 Tx power consumption of implantable BMIs in various works

#### 1.2 Data Compression

#### 1.2.1 Introduction and trade-offs

As will be discussed in the remaining of this chapter, there are several ways to reduce/compress the size of data. However, while the ultimate goal is to achieve the highest compression ratio (CR), this must not come at the cost of losing valuable data.

For some applications it is possible to significantly reduce the required Tx's throughput by only transmitting the outcome of on-chip signal processing instead of the raw recorded data. In the extreme case, the entire signal processing could be done on-chip so that only the result (e.g., a one bit signal showing a classification output) needs to be transmitted. While this has the potential to reduce the data size by orders of magnitude and practically solves the problem, as discussed in [40], for many cases it is desired to transmit the raw (i.e., unprocessed) data (e.g., when processing algorithm is too computationally expensive to be done on-chip, or for physician's future review), demanding the data compression technique not to be specific to an application.

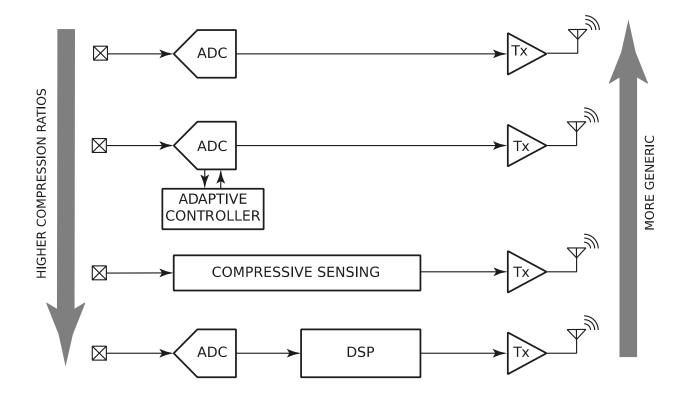

Figure 1.3 Simplified block diagram of different generic and application-specific methods used for data reduction in implantable BMI devices.

Figure 1.3 shows some of the most popular approaches used for data acquisition in neural recording devices, and where each of them stands on the spectrum of achieved compression ratio vs. generality of the approach. Basically, one end of the spectrum is to send the raw data, without performing any form of compression, while the other end is to perform extensive data processing on the acquired data and transmit only specific features of the data, which makes it the least generic. Techniques such as compressive sensing or adaptive compression (e.g. adaptive sampling) stand somewhere in the middle of this spectrum. As will be discussed, among the two, compressive sensing achieves a higher CR but is less generic compared to adaptive compression techniques. Besides CR, data loss, and generality of the technique, reconstruction accuracy in the receiver, and the required on-chip computational power for conducting the compression are critical parameters that must be considered when choosing data compression method.

#### 1.2.2 Information sparsity

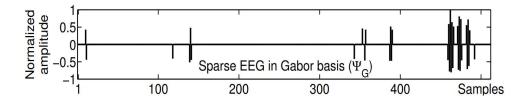

Figure 1.4 EEG signal sparsity in wavelet domain [15]

In many applications, data sparsity is the key characteristic that is widely leveraged of in many compression techniques. A data is said to be sparse in a certain domain (i.e. time, frequency) when most of the signal's magnitudes in that domain, are either zero, or insignificant. As an example, Figure 1.4 shows an EEG data is sparse in Gabor basis, as it contains very few non-zero values; or a sine wave is said to be sparse in frequency domain, as it only has one non-zero component in that domain.

Sparsity in bio-signals can be defined in an another way as well. A bio-signal is information sparse meaning, in time-domain, biologically meaningful events (e.g., epileptic seizures in an iEEG recording) are inherently unpredictable and happen infrequently.

#### 1.2.3 Compressive sensing

Compressive sensing (CS) is a compression technique used widely in applications such as image processing, radar, video coding and many more [23] [24] [25]. This method can be considered more on the generic side of the spectrum, since it can be performed on any signal that have sparsity in at least one domain. A key advantage of this technique is that it allows for power-friendly implementation as in this method, compression is done in the time domain, regardless of the domain of sparsity.

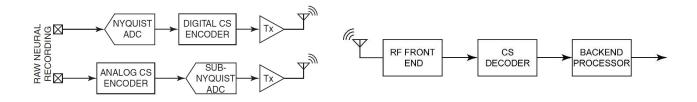

Figure 1.5 Block diagram of a typical CS tranmitter and reciver

In this method, unlike conventional data acquisition methods, in which data is acquired and transmitted at a rate at least two times the highest frequency component of the signal (the Nyquist-Shannon rate), data is compressed and reduced proportional to the amount of information it carries in its domain of sparsity [26], promising significantly lower amount of data needs to be transmitted for lossless signal reconstruction [26] [27].

CS is conducted by projecting the Nyquist rate sampled data X, which holds  $X_{N\times 1}$  samples, to its compressed version  $Y_{M\times 1}$ , which will have M samples, where M<<N. The projection is done through multiplication of  $X_{N\times 1}$  by a "measurement matrix"  $\phi_{M\times N}$ , resulting in a compressed version of  $X_{N\times 1}$  called  $Y_{M\times 1}$ .

Implementation of the encoding circuit can be done in either digital or analog domain (Figure 1.5), using a set of mixers and integrators, which despite seemingly complicated computational procedure of the method, makes the technique power friendly for on-chip implementation. Works done in [29], [30] have implemented the technique in the digital domain, whereas, works done in [26], [28], [31] offer an analog based compressed sensing. Generally, for wireless sensor application, it is shown that digital based compressive sensing implementation achieves better power efficiency [27].

In this technique, data reconstruction procedure consists of a set of complex power hungry computations. However, for implantable BMIs, receiver is outside of the body and has far less

constraints in terms of computational power and energy budget [26], so this might be a less critical disadvantage.

The key drawback of CS is that conducting any non-trivial signal processing on compressivelysensed signal is infeasible before it is decompressed (i.e., decoded) in the receiver. In many implantable devices developed for diagnostic and closed-loop responsive treatment, it is critical for the BMI to conduct signal processing on chip (e.g., to minimize the processing delay) [2][13][32][38]. However, the compressed signal is far too modified to perform any signal processing on it.

#### 1.2.4 Adaptive sampling

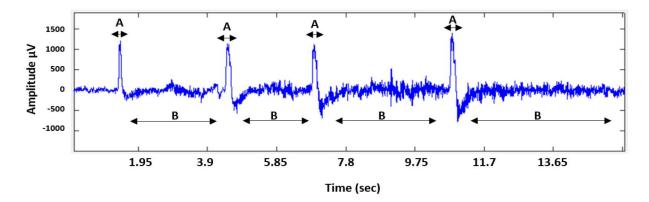

Adaptive sampling is another popular method of compression which relies on the sparsity of events occurrence in bio signals. As shown Figure 1.6, during periods "A", a significant event happens, whereas during periods "B", signal is almost idle and holds no neurologically-relevant information. Considering the high likelihood of sparsity in bio-signals, adaptive sampling suggests adjusting the sampling rate in real time and according to the signal's level of activity. This allows for sampling with Nyquist rate during periods with high level of activity and with a sub-Nyquist rate for the rest of time. Considering the overwhelming dominance of the "idle" periods compared to the high-activity periods, this results in a significant reduction in the acquired data volume, and consequently, the required throughput for wireless Tx. The word adapativeness comes from the fact that, each BMI's recording channel continuously adjusts its sampling rate according to signal's level of activity, therefore, making the power consumption, also adaptive to the events occurrence.

Figure 1.6 EEG signal with events periods marked as A and idle periods as B

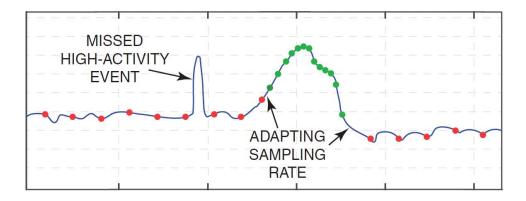

An important challenge in adaptive sampling is accurate identification of high-activity periods. Thresholding is one the methods in which the incoming signal's amplitude is compared to a set of pre-set thresholds to evaluate the magnitude of deviation from the signal's baseline and adjust the sampling rate accordingly, as illustrated in Figure 1.7. This method's performance is highly sensitive to proper selection of threshold values. A too-small threshold value could lead to identifying the majority of the recording as "high activity", hence achieving little to no data compression, while a too-large threshold could result in missing important neurological events.

The relatively-high chance of missing all or part of a neurological event is in fact one of the major drawbacks of adaptive sampling. This is due to the fact that sampling rate is set according to the N previous samples. Therefore, for any event that follows a long period of idleness, there is a high chance that part or all of it is missed due to the latency in adjusting sampling rate. Figure 1.8 illustrates this drawback graphically. As shown, while events with long period are almost fully captured, the shorter events are completely missed, making the method unreliable for applications where missing even one event could lead to severe consequences.

Figure 1.7 Concept of adaptive sampling

Figure 1.8 An example of missing short high-activity periods in adaptive sampling

#### 1.3 Adaptive resolution

The mentioned problem with adaptive sampling motivates us to look for another compression technique which can eliminate the risk of information loss, while still being able to leverage from signal's information sparsity, i.e., adaptively adjust the data rate according to the amount of vital information signal holds. The technique that is proposed here, is adaptive resolution compression. In this technique unlike adaptive sampling, sampling rate is always kept at Nyquist rate, and alternatively only the resolution of the sampled data varies. This way, while the bit rate is reduced, there will be no risk of losing either short or long-period events. Figure 1.9 depicts the difference

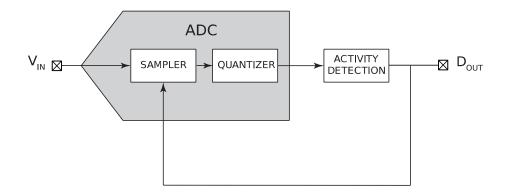

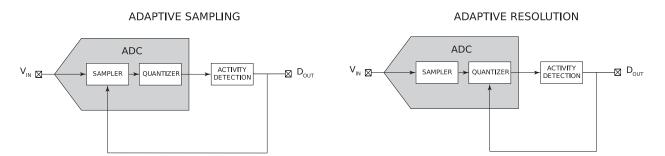

Figure 1.9 Conceptual difference between adaptive sampling and adaptive resolution techniques

between the concept of adaptive sampling, which was explained in section 1.2.4, and adaptive resolution discussed here. As shown, the main difference here is that the feedback signal which is the result of event detection, is fed to ADC's quantizer rather than the sampler, resulting in changing the quantization resolution and keeping the sampling rate at Nyquist. While the difference between the two methods looks minor and simple, implementing an adaptive resolution scheme introduces several challenges and complications in terms of designing a compatible front-end, efficient design of a variable data converter, a loss-less event detection unit, and a low-latency resolution adaptation controller. It should be mentioned although the focus of this work is on neural signals, however, this compression technique is applicable for any sort of signal containing some sort of information sparsity or event sparsity in time-domain. As an example, many types of events in bio-signals other than neural signals such as; ECG, EMG, etc., show this type of sparsity and therefore the technique generality is not only applicable to various type of neural events but also it is expandable to other types of bio-signals.

It should be mentioned that in addition to power saving through reducing total number of transmitted data, the constraint on bandwidth through this compression will be relaxed as well. To elaborate, because of reduction in overall number of data for a fixed duration compare to when the

technique is not used, data can be transmitted at a lower bit rate and therefore reducing the required bandwidth for transmission.

#### 1.4 Thesis Organization

Chapter 2 will focus on the system-level implementation of the adaptive resolution compression technique, and includes system-level simulation results illustrating the proposed idea's efficacy in improving the recording system's energy efficiency. Chapter 3 will discuss the detailed implementation of the digital backend modules responsible for high-activity event detection, signal baseline calculation, and responsive resolution adjustment. These modules are integrated on a silicon IC and fabricated. The physical layout and experimental setup for this IC are also presented in this chapter. Chapter 4 will discuss the design procedure, detailed transistor-level implementation, and system- and circuit-level verification of a novel mixed-signal fully-dynamic-power neural ADC developed as the recording front-end module for the presented system.

# Chapter 2 System-Level Implementation

As discussed in chapter 1, the main focus of this work is to improve the energy efficiency of the implantable device by adapting its recording accuracy to the input signal's level of activity, without any meaningful loss of data. In this chapter, in order to understand the principles of the proposed idea, first, a few key definitions will be explained, and then the working principles of the mixed-signal front-end and the digital backend of the proposed architecture will be presented. In the end, the MATLAB simulation results and the potential efficacy of the proposed technique will be discussed.

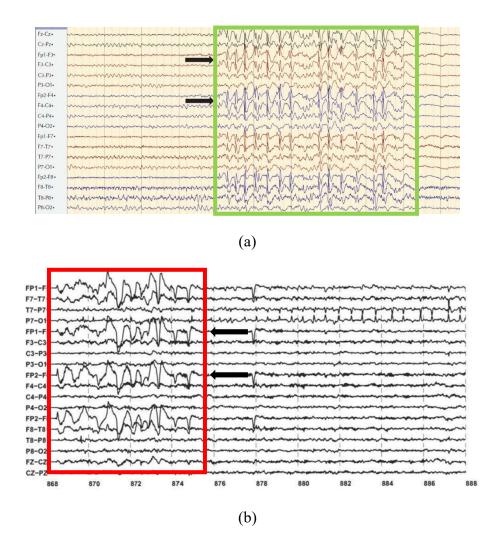

Figure 2.1 An example of (a) high-activity event (b) noise interferences that unwantedly are detected as a highactivity event[39]

#### 2.1 Background Theory

#### 2.1.1 Events in Neural Recording

In this work, an event (or interchangeably a "high-activity event") is defined as when the timedomain amplitude of the neural signal experiences a considerable (i.e., above a predefined threshold) deviation from the "baseline", which is the average signal level during idle (i.e., no event) periods, Figure 2.1 (a). While these "high-activity" episodes could be due to many reasons such as background noise, interference, motion artifacts, stimulation artifacts, etc., their appearance could also be associate with neurologically-relevant events such as an epileptic seizure, as shown in Figure 2.1 (b). If the threshold for identifying a period of the signal as a "high-activity event" is set low enough, it could be claimed with high certainty that the idle periods do not contain any critical information about neurologically-significant episodes, hence, capturing them with low accuracy will not result in any loss of critical information. Considering the information sparsity of neural signals in the time domain (in terms of the occurrence rate of "high-activity events"), this allows for a significant reduction in the required power for data acquisition as well as the required throughput for data transmission. Of course, the success in both keeping the data integrity and power/resource reduction heavily depends on how well the event thresholds are set. We will discuss the strategy and mechanism for threshold selection in due course.

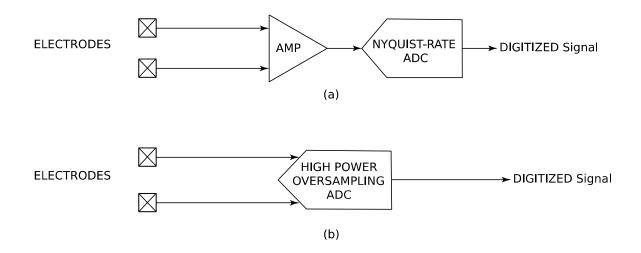

#### 2.1.2 Neural ADCs

The main tasks of the circuits designed for recording brain's neural activity are low-noise signal amplification and quantization. Once a neural signal is amplified and digitized, various types of signal processing could be performed on it. This is why conventional neural recording channels consist of a low noise amplifier and an ADC, as shown in Figure 2.2 (a). Despite the early success of this conventional approach, it was shown not to be suitable for massive integration (i.e., hundreds or thousands of recording channels on one chip) mainly due to the required silicon area for its implementation [13].

To overcome the power scalability issues, various types of ADC are proposed for neural recording such as nonlinear, predictive or level-crossing ADCs. In [44] a nonlinear ADC introduced in which through an interior anti-log ADC, non-uniform quantization is achieved to reduce the amount of bit rate transmission. In [45], a predictive scheme is used to implement the

predictive ADC. In this ADC by predicting the incoming signal through the previous samples, incoming sample digital conversion in the SAR ADC is switched and done for a sub-range instead of digital full-scale range. This way, unlike previous ADC which reduces the power consumption through the reduction of data rate, the ADC power itself is scaled by burning lower power for when conversion is done in sub-range. In [46] another popular type of ADC called level-crossing ADC is used, in which output is generated each time signal passes a pre-set level along with the timing duration between two consecutive samples. The sampling in this type of ADC is done in a non-uniform way and its power consumption depends on the rate of signal's variations.

Another type of ADC which has become popular in recent years for neural recording channels is neural ADCs or direct ADC architectures. In this type of neural recording front-ends (shown in Figure 2.2(b)), unlike conventional ones, both processes of signal amplification and digitization are performed in a single oversampling ADC stage. It has been shown that by avoiding the analog low-noise amplifiers and relying on the mixed-signal architecture of these ADCs, high-precision neural recording could be performed without the need for bulky non-scalable passive components (e.g., input capacitors used for AC coupling) [32]. Additionally, these oversampling ADCs are capable of achieving very high resolutions (e.g., >14 bits), at a reasonable power budget, particularly for applications that have a low input frequency bandwidth (i.e., a few kHz) such as neural signals. This allows for achieving a very high dynamic range for the recording circuit, which is a critical requirement if simultaneous recording and stimulation is to be conducted [33][58]. Most importantly for the purpose of this work, the power consumption of direct ADC architectures is fully dynamic, unlike the case for conventional architectures where the majority of the recording channel's power consumption was due to the static power of the low noise amplifier. This means

Figure 2.2 (a) conventional and (b) direct-ADC recording front-end concepts.

that if the ADC's precision, hence its power consumption, is made adaptive to the input signal's level of activity, the power saving benefit is

applicable to the entire recording channel, and not just a small portion of it (as in conventional architectures).

#### 2.1.3 Adaptive Resolution vs. Adaptive Sampling

Prior to discussing implementation, it is important to clearly distinguish between the widely known concept of adaptive sampling and the proposed concept of adaptive resolution.

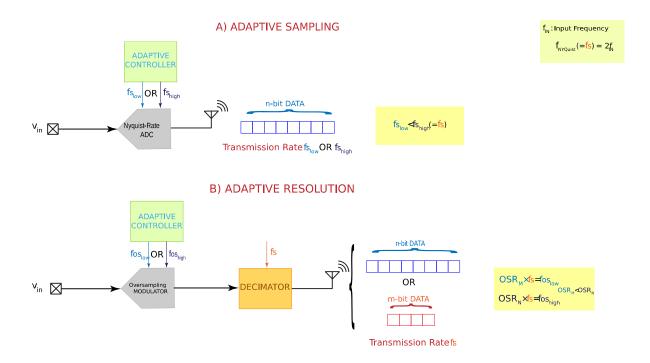

As shown in Figure 2.3(a), in adaptive sampling, the controller adjusts the system's, sampling rate to capture the input signal with at least two different sampling frequencies of  $f_{S_{low}}$  and  $f_{S_{high}}$ , with  $f_{S_{high}}$  being a super-Nyquist frequency. If the controller recognizes that the input signal holds vital information, system will switch from  $f_{S_{low}}$  to  $f_{S_{high}}$ , and since  $f_{S_{high}}$  is set to at least the Nyquist-rate ( $f_{S_{high}} \ge f_{Nyquist} = 2f_{IN_{MAX}}$ ), all the information within the signal is captured. If the controller doesn't detect an upcoming important event, the system's frequency is switched back to  $f_{S_{low}}$ , which is set at a sub-Nyquist-rate ( $f_{S_{low}} < 2f_{IN_{MAX}}$ ), and therefore, signal is not

Figure 2.3 Comparison between adaptive sampling and adaptive resolution techniques

fully captured. This data loss is acceptable since the input signal during idle periods is not carrying valuable information.

As shown in Figure 2.3(a), the transmitter also sends data packages according to the two sampling rates. Therefore, for the idle periods, which are expected to be the majority of the neural recordings, the transmission rate, hence the transmitter's power consumption is reduced according to the sampling rate reduction. As discussed in Chapter 1, since transmitters are the most power consuming block of the implantable device, this power saving is significant and could enable the integration of many more recording channels on the chip for the same power budget. However, as it was mentioned in previous chapter, this method is not the best compression technique candidate for situations where there are short-period high-activity events, as system could completely miss that type of activity due to sub-Nyquist sampling, which could have dire consequences for devices with diagnostic applications.

The aforementioned problem, motivated the proposed technique called adaptive resolution. In this technique, instead of varying the sampling rate, quantization resolution adapts to the input signal's level of activity. Figure 2.3(b) depicts a high-level implementation of this idea using an oversampling ADC, which are particularly advantageous for implementation of a variable-rate data converter because they require the same low-resolution quantizer (e.g., in most cases a singlebit quantizer such as a voltage comparator) irrespective of their targeted resolution. Indeed, the quantization resolution in these ADCs are set by the oversampling ratio (OSR) and the order of the loop filter. As such, by changing the clock frequency of the modulator, and without changing the quantizer, the quantization resolution could be varied dynamically. As such, the resolution variability comes at almost no extra power or area cost and no component overdesign.

In contrast, for Nyquist-rate ADCs (e.g., a SAR ADC), the quantizer architecture and its components specifications, particularly those with static power consumption, (e.g., settling time of an OpAmp used for successive approximation) are set by the highest targeted resolution and reducing the resolution will not result in a proportionate power reduction. This comes at the cost of extensive area and power overdesign, since for most of the time the recording system operates in low resolution mode, due to the sparsity of high-activity events in neural signals.

In addition to the aforementioned problem, in Nyquist-rate ADCs, the resynchronization and reconstruction of the sampled data with different resolutions is a complex task in the receiver, whereas in oversampling ADCs, all that needs to be done is to sync the decimator with the variable OSR, as will be described later.

In Figure 2.3(b), the incoming data ( $V_{IN}$ ) is either sampled with a high oversampling frequency  $(f_{OS_{high}})$  or a low oversampling frequency  $(f_{OS_{low}})$ . In an oversampling ADC, there is a direct relationship between OSR and oversampling frequency ( $f_{Nyquist} = 2f_{IN_{max}}$ ,  $f_{OS} = OSR \times$

$f_{Nyquist}$ ). Also, there is a logarithmic relationship between the oversampling frequency and SQNR as shown in (2.1)

$$SQNR = 3.01 \times K \times (2L+1) - 9.36L - 2.76, \tag{2.1}$$

Where

$OSR = 2^{K}$  and L = Order of modulator

Therefore, by modifying the OSR, different sampling resolutions can be achieved. As shown in the figure, prior to being fed to the wireless transmitter, the output of the modulator is passed through a decimation filter resulting in the removal of high-frequency out-of-band noise and reducing the data rate to the Nyquist-rate. In this way, regardless of the resolution, unlike adaptive sampling, data packages are sent at Nyquist-rate ( $f_{nyquist}$ ), and only size of each package is modified. Here, since data is oversampled with 2 different resolutions, there are some consideration that should be taken into account in designing the decimation filter, which will be discussed in the next section.

It should be noted that while we described both adaptive sampling and adaptive resolution concepts with only two levels (for the sake of simplicity), both techniques could be implemented in a more sophisticated way where multiple levels of sampling rate or resolution are employed.

Adopting the proposed strategy can significantly reduce the required transmitter's throughput, hence, the wireless transmitter power consumption. Applying this method to each recording channel, can further reduce the system's overall power consumption, while assuring all neurologically-relevant events are captured.

#### 2.2 Functional Implementation

Implementation of the proposed technique is divided into two parts, the digital back-end, and the mixed-signal front-end. Each will be explained separately in the following sections.

#### 2.2.1 Digital Back-End

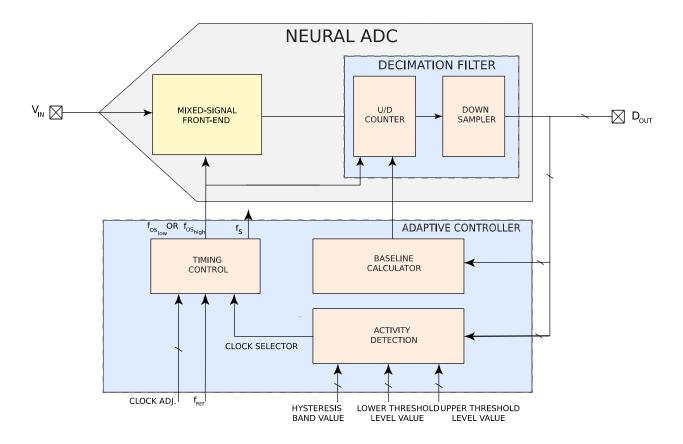

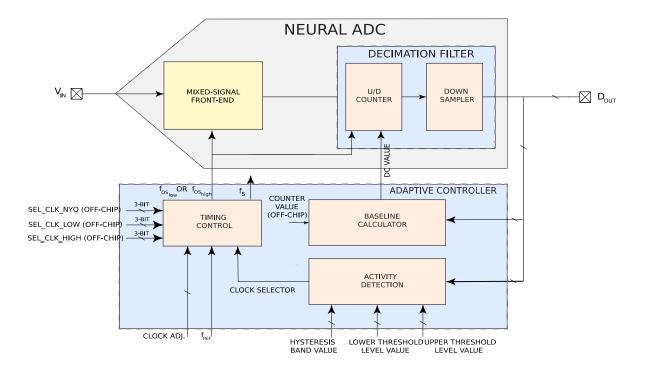

Figure 2.4 depicts the top-level block diagram of the proposed adaptive-resolution neural ADC and the detailed block diagram of the digital backend units, which are the decimation filter (i.e., the N-bit Up/Down Counter + Down Sampler) and the adaptive controller. As shown, the controller receives the ADC's output as the input and decides for one of the two clock frequencies (i.e.  $f_{OS_{high}}$  and  $f_{OS_{low}}$  in Figure 2.3 (b)) to be selected as the output.

The controller itself consists of an activity detection unit for identifying high-activity events in the neural signal, a Clock Selector unit for adjusting the oversampling frequency based on the input signal's level of activity, and a Baseline Calculator unit for tracking the DC level of the input signal and calibrating the activity detection accordingly. In the following section, these units are explained in detail.

Figure 2.4 Internal block diagram of the digital backend blocks of the proposed adaptive-resolution neural ADC.

#### 2.2.1.a Decimation Filter

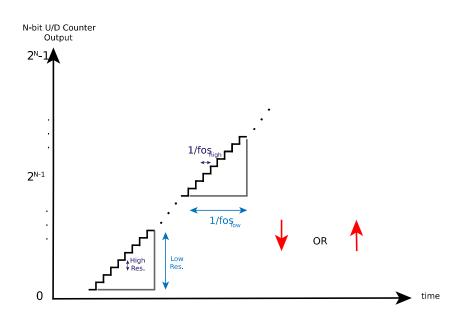

As discussed previously, in order to reconstruct signal's quantized amplitude at Nyquist frequency, the modulator's output bitstream needs to get averaged and down sampled (i.e., decimated). In the frequency domain, the combination of these two steps is similar to applying a low-pass filter with a cut-off frequency at the signal's bandwidth ( $f_{INMAX}$ ). In the presented system, the decimation is implemented by (a) using an N-bit up/down (U/D) counter, which its output value increases/decreases based on the modulator's bitstream (i.e., increases with a 1, and decreases with a 0), and (b) reading out the counter output every OSR clock cycles. This is equivalent to applying a moving average filter to a series of one-bit numbers (modulator's output bitstream which has a bandwidth of  $f_{OS} = OSR \times 2f_{IN}$ ), and having an output for every OSR input value.

Given that for each resolution there is a specific OSR value to be able to decimate different resolutions, the U/D counter should be designed for the highest aimed resolution (refer to figure 2.6(b), in which N is the highest resolution bit count). For lower resolutions, along with oversampling frequency, counter's counting step size also should be adjusted, meaning that if for high resolution, counter increase or decrease its output value by 1 bit, for low resolution case, counter needs to increase/decrease the value by  $2^{M}$ , where M is the lower resolution bit count ( refer to Figure 2.3 (b)).

A down sampler reads the output of the counter at the corresponding OSR rate ( $OSR_M$  for low oversampling rate or  $OSR_N$  for high oversampling rate), as shown in Figure 2.3(b). In addition, signal's baseline in analog domain (i.e. 0V) is the middle value of counter in digital domain, i.e., for an 8-bit counter, digitized signal's baseline is 128(i.e., 8'b10000000). This way negative voltage values in analog domain will be translated into 0-127 range (i.e., 8'b00000000 to 8'b0111111) of counter's range, and for positive values, from 129 to 255 (i.e., 8'b10000001 to 8'b1111111). Figure 2.5, depicts the explained mechanism more clearly.

Figure 2.5 Output of the N-bit U/D counter; counter is designed for the high resolution; the lower resolution is achieved by increasing the UP/DOWN counting step size.

#### 2.2.1.b Baseline Calculation

A baseline calculator unit is also designed and included in the system that continuously calculates the DC level of the input signal and adjusts the signal fed to the activity detection unit to have a relatively constant DC level. The baseline is calculated as,

$$DC_{new} = \frac{1 \times C + W \times DC_{old}}{1 + W}$$

(2.2)

where C represented the output of the N-bit U/D counter,  $DC_{old}$  is the previously calculated DC value, and W is an adjustable coefficient that decides how much weight we assign to the current DC value compared to the new data point (i.e., C) in calculating the new DC value. It should be mentioned that the baseline calculation is done every "A" cycles, where A is also adjustable by the user depending on the variability of the input signal.

The obtained  $DC_{new}$  is then subtracted from the counter's output, to maintain a relatively constant DC level for the signal fed to the activity detector. This unit is crucial as the down sampled

signal is compared to a set of fixed threshold levels. By adjusting the signal's baseline before feeding it to the activity detector, we effectively turn the fixed thresholds into dynamic threshold values that adjust themselves according to the signal's DC level.

### 2.2.1.c Activity Detection

As mentioned in section 2.1, the high-activity events detection is done using dynamic thresholding. Also, as discussed, accurate selection of the threshold values is critical in striking a better trade-off between minimizing data loss (i.e., no event loss) and maximizing the energy efficiency (i.e., maximum data compression). As shown in n Figure 2.4, the decimated data is continuously fed to the activity detection unit and is compared to the pre-set threshold levels by user. In order to prevent unnecessary clock adjustment due to noise/interference that might look like a high-activity event, the system employs a set of hysteresis band, along with the threshold levels, which are customizable by the user.

The output of activity detection unit, which essentially is a one-bit command signal, is send to the timing control unit. The clock selector unit generates the oversampling frequencies ( $f_{OS_{low}}$ , or  $f_{OS_{high}}$ ) used in the system, and according to the result of the activity, chooses which clock frequency is sent to mixed-signal front-end.

### 2.2.2 Mixed-Signal Front-End

The mixed-signal recording front-end of the proposed system is a neural ADC, which as mentioned earlier, is built based on principles of oversampling ADCs. By implementing the recording front-end as a neural ADC, besides the inherent benefits of neural ADCs, (e.g., high DR, area and power efficiency, etc.), we leverage the fact that the entire front-end (i.e., amplification and digitization) is implemented in a single block with a fully dynamic power consumption.

Therefore, the proposed adaptive variation of oversampling clock frequency will result in adapting the power consumption of the entire recording front-end, and not just the quantizer.

To put this into perspective, with a conventional recording front-end architecture (i.e., amplifier + ADC), the amplifier has a static power consumption and any adaptivity in the ADC's sampling rate or resolution could only save part of the ADC's power, which is typically 10-20% of the total front-end power. While each recording front-end has a very small power consumption, recent works report close to 100 copies of these circuits integrated in an IC and the research community's target is to integrate hundreds to thousands of recording channel in each IC in the future. Taking that into account, a front-end architecture with fully-dynamic power that is adaptive to the input neural activity seems to become increasingly important in enabling potential scalability of future implantable neural interface microsystems.

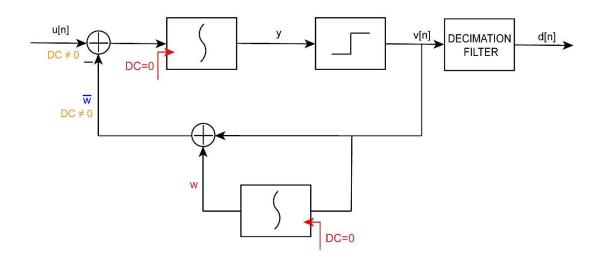

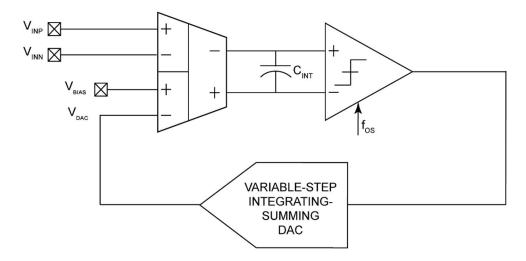

The proposed front-end architecture is aimed to achieve a maximum 8-bit recording resolution, while being able to handle large (e.g., 50mV) DC offsets and artifacts at the input. Figure 2.6, depicts the proposed ADC's block diagram, which is a combination of a  $\Delta$ - and a  $\Delta\Sigma$  modulators. Compared to a conventional  $\Delta\Sigma$  modulator, an integrator is added in parallel with the feedback path. Therefore, the quantized output is first integrated before being fed back to the subtractor at the input. Due to the inherent low-pass behavior of the integrator in the feedback, its output ( $\overline{w}$ ) is expected to contain the DC and low-frequency content of the quantized signal. When  $\overline{w}$  is subtracted from the input (u[n]), the input's DC is blocked and its low-frequency content is attenuated, effectively resulting in a high-pass transfer function for the overall system, which allows for high-frequency content such as the difference between two consecutive input samples

Figure 2.6 system-level diagram of the proposed  $\Delta$ - $\Delta\Sigma$  front-end architecture

(hence, the additional  $\Delta$ ) to pass. Also, as shown, given that any DC at the input of an integrator results in its output saturation, the negative feedback structure ensures that the DC at the input of both integrators is always maintained at zero.

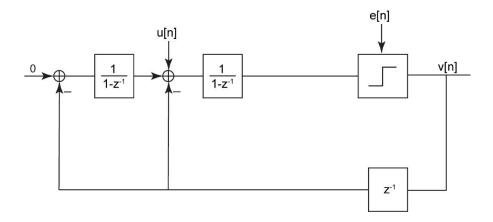

Figure 2.7 Block diagram of the proposed  $\Delta$ - $\Delta\Sigma$ ADC

More important than the DC removal, the addition of the feedback integrator results in further shaping the in-band quantization noise by another order. Figure 2.7 shows the z-domain block

diagram of the presented ADC. Based on this block diagram, the signal transfer function (STF) and the noise transfer function (NTF) of the presented ADC can be written as,

$$STF(z) = \frac{V(z)}{U(z)} = \frac{\frac{1}{1-z^{-1}}}{1+\frac{z^{-1}}{(1-z^{-1})^2} + \frac{z^{-1}}{1-z^{-1}}} = (1-z^{-1})$$

(2.3)

$$NTF(z) = \frac{V(z)}{E(z)} = \frac{(1-z^{-1})^2}{(1-z^{-1})^2 + z^{-1}(1-z^{-1}) + z^{-1}} = (1-z^{-1})^2$$

(2.4)

The NTF equation shows the second-order filtering of the quantization noise, while the STF shows the  $\Delta$  modulation and that the signal is differentiated (i.e.,  $(1 - z^{-1})$ ), hence its DC is removed.

To efficiently implement the proposed design, the proportional and the integrative feedback paths can be combined into a single path using the algorithm described below. The result of the summation of the two feedback paths in Figure 2.6 for a random output v[n] is shown in Figure 2.8. As annotated in the figure, v[n] represents the quantizer output, w represents the integration of v (increases by one for v=1 and decreases by 1 for v=0), and  $\overline{w}$  represents the sum of the two (i.e., v+w).

| ~            | 1274 - 1277  |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

|--------------|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| +            | <b>w</b> = 1 | 2 | 3 | 2 | 3 | 4 | 3 | 2 | 3 | 2 | 3 | 4 | 5 | 4 | 3 |

| $\checkmark$ |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|              | <b>w</b> = 2 | 3 | 4 | 1 | 4 | 5 | 2 | 1 | 4 | 1 | 4 | 5 | 6 | 3 | 2 |

Figure 2.8  $\overline{w}$  results for random output bit sequence ( for  $\overline{w}$  calculation bit 0 is equivalent to -1)

The changes follow the pattern shown in table 2.1. Based on the output's two consecutive bits (v[n] and v[n-1]) there are four different possibilities on how the value of  $\overline{w}$  changes. For instance, the sequence of "00", decrease the value of  $\overline{w}$  by 1 step size (-1), and the sequence of "01" increase  $\overline{w}$  by 3 step size (+3). By using this algorithm, the two paths can be merged into as a single path.

Table 4.1  $\Delta \overline{w}$  for the four possible outcomes based on v[n] and its previous value v[n-1]

| v[n-1] | v[n] | $\Delta \overline{\mathbf{w}}$ |

|--------|------|--------------------------------|

| 0      | 0    | -1                             |

| 0      | 1    | 3                              |

| 1      | 0    | -3                             |

| 1      | 1    | 1                              |

Since the feedback signal is subtracted from the analog input, the digital step size variations must be converted to analog as well. This means a reference voltage step size should be chosen, and the step size variations (in this case  $\pm 1$  or  $\pm 3$ ) are applied based on that. The process of choosing the reference step size depends on three parameters: the maximum input signal amplitude  $(A_{IN})$ , the maximum input signal frequency  $(f_{IN_{max}})$ , and the oversampling frequency  $(f_{OS})$ . In order to make sure that the input signal is tightly tracked by the feedback path, the step size should be selected based on the slope of the input signal (which depends on both  $A_{IN}$  and  $f_{IN}$ ) in a way that the difference between u and  $\overline{w}$  is neither too large (low quantization resolution), or too small (slope overload).

Based on this, the relation between reference step size and the three mentioned parameters can be obtained as following

$$Signsl's Slope_{max} = \frac{d}{dt} A_{IN} \sin(2\pi f_{IN} t)_{t=0} = -2\pi A_{IN} f_{IN}$$

(2.5)

$$|-2\pi A_{IN}f_{IN}| < \frac{\text{Refrence step size}}{\frac{1}{f_{OS}}} \to \frac{2\pi A_{IN}f_{IN}}{f_{OS}} < \text{Reference step size}$$

(2.6)

Expression (2.5) is the maximum slope of a sine wave. In order for the integrating step sizes to follow input signal closely and to prevent slope overload, integrated step size value for each sampling duration  $(\frac{1}{fos})$  should be bigger than the maximum slope of signal. This way the lower bound for the reference step size is defined (2.6). The upper bound for the reference step size value is also set in a way that it is close to target resolution LSB value. Through result of test simulations, to obtain desired SNR from the modulator, the upper bound value shouldn't be more than 1.5 times of the lower bound value.

### 2.3 MATLAB Simulation Results

The described system was implemented in MATLAB and its efficacy in improving the system's energy efficiency was investigated. In this section, first the MATLAB-based functional implementation of the proposed mixed-signal front is described and simulation results showing its second-order noise-shaping behavior are presented. Next, the functional implementation of the presented adaptive resolution scheme is presented and its effectiveness in improving energy efficiency through loss less data compression is demonstrated using recordings from the CHB-MIT scalp EEG database as test signals [35].

In this system, we picked the two target resolutions to be 8-bit for high resolution recording and 4-bit for low resolution. As discussed previously, these are arbitrary values and the proposed adaptive resolution scheme could be used with more levels of resolution, each set to an arbitrary number. The SQNR of a generic  $\Delta\Sigma$ -ADC with order L was shown in (2.1). In addition, the general SQNR for any type of ADC with N-bit resolution is:

$$SQNR = 6.02N + 1.76 \tag{2.7}$$

Using (2.1), and (2.7), and considering an L=2, the oversampling frequencies  $f_{os_{low}}$ , and  $f_{os_{high}}$  required for the target resolutions are obtained as

Considering that the maximum input signal's frequency  $(f_{IN})$  is 500Hz, both  $f_{os_{low}}$ , and  $f_{os_{high}}$  can be calculated with respect to the obtained OSRs.

$$f_{\text{os}_{high}} = OSR \times 2 \times f_{IN} = 32kHz \tag{2.10}$$

$$f_{0S_{high}} = OSR \times 2 \times f_{IN} = 8kHz$$

(2.11)

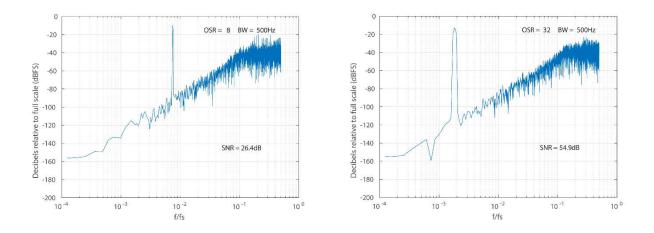

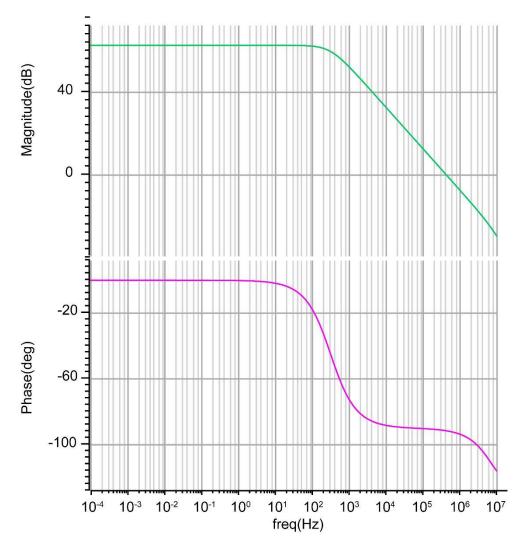

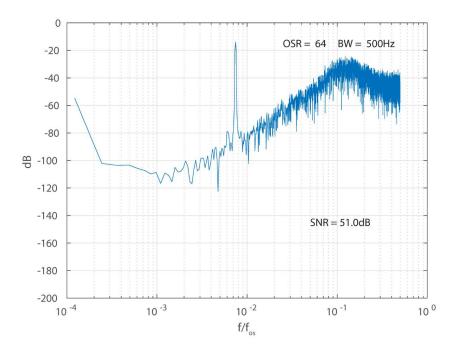

Figure 2.9 depicts the frequency response of the proposed mixed-signal front-end that is tested with the calculated oversampling frequencies (input signal at 60Hz). The figure on the left shows the result for the case when the system is operating with high resolution. i.e. 8-bit mode, and the figure on the right shows the case that the system operates in the low resolution mode, i.e. 4-bit. As shown, the system shows a 2<sup>nd</sup> order noise shaping, where noise is pushed to the out-of-band

Figure 2.9 Frequency response of the proposed mixed signal front-end in MATLAB, for 4-bit and 8-bit resolution from left to right

frequencies by a slope of 40dB/decade. Also, the calculated SQNR, for each resolution, corresponds to the calculated SQNR in (2.8) and (2.9).

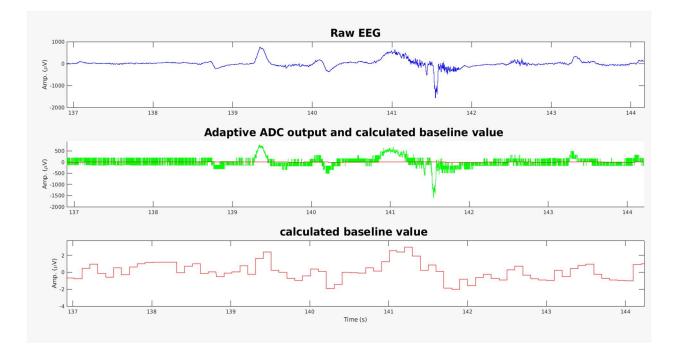

The result of MATLAB simulations of the mixed-signal front-end and digital back-end is shown in Figure 2.10. The blue signal is the raw EEG fed to the system, and the green signal is the output of the presented ADC, sampled with two different resolutions. As shown, when signal's amplitude is higher than a certain threshold level, green waveform closely tracks the original due to the employed high resolution. In contrast, when amplitude is lower than threshold, green waveform coarsely follows the signal due to the lower clock frequency utilized by the modulator. In addition, the red waveform depicts the baseline calculator result which is updated regularly. From the plot, it can be seen DC value is around 0V, meaning ADC's output is also kept around the baseline.

Figure 2.10 EEG signal (top), the reconstructed output with adaptive resolutions (middle), and the automatically calculated baseline (bottom).

In order to determine the efficiency of the method, a set of EEG recordings from CHB-MIT database, each containing a seizure event, are fed to the system. We expect not to miss any of the seizure events as they all are counted as high-activity events, hence, must be recorded with high resolution.

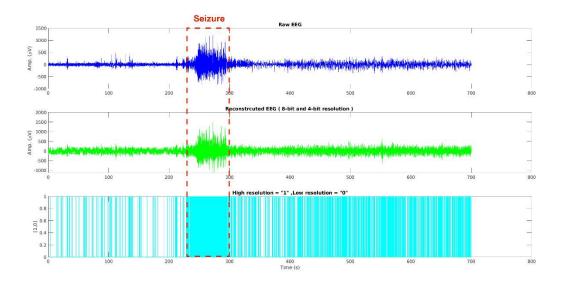

Figure 2.11 depicts the result of digitization (middle) of 10 minutes raw EEG signal (top), with two different resolutions (bottom). In the bottom plot, "0" corresponds to time periods signal was sampled in low resolution, and "1" corresponds to when it was sampled in high resolution. The seizure episodes are marked on the plots. When the signal is in low activity region, meaning it's lower than threshold level, it is sampled with low resolution, whereas, when the signal is out of this region, it is sampled with high resolution

Figure 2.11 An example of system's response to an EEG signal with seizure

Table 2.2 presents the total value of "1" s and "0" s as well as the percentage of their occurrence during seizures and non-seizure periods of the signal in Figure 2.11. As shown, the test signal was sampled with high resolution (8-bit resolution) for only 20% of the total time, and for the rest, the system operated in low-resolution mode. In addition, for more than half of the time high resolution sampling occurred during the seizure. Also for more than 90% of the total low resolution sampling durations, signal had no seizure. This shows the proposed model behaves as expected, i.e., system's sampling resolution is adaptive to events occurrence.

Table 2.2 Statistical summary of the simulation results presented in Figure 2.11.

|                 | high resolution mode = $20\%$ | Total % in low resolution<br>sampling mode = 80% |                     |  |  |  |

|-----------------|-------------------------------|--------------------------------------------------|---------------------|--|--|--|

| % in<br>Seizure | % in<br>Non-Seizure           | % in<br>Seizure                                  | % in<br>Non-Seizure |  |  |  |

| 53%             | 47%                           | 6%                                               | 94%                 |  |  |  |

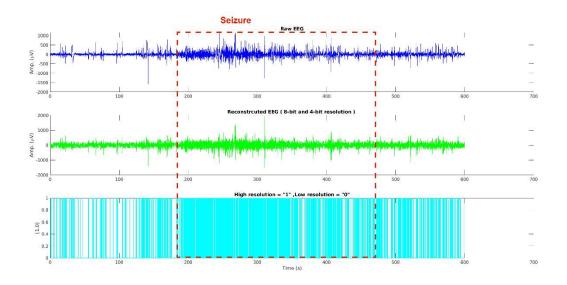

Figure 2.12 An example of the proposed system's response to an EEG signal containing a seizure episode.

Figure 2.12 shows system's output for another EEG test signal containing another seizure. Similar to the previous result, it can be seen in Table 2.3, more than half of the high resolution mode is happening within the seizure region, and in total for more than 70% of the total time the system is operating in low resolution mode.

Table 2.3 Statistical summary of the simulation results presented in Figure 2.12.

| high resolution | Total % in low resolution         |                                              |  |  |

|-----------------|-----------------------------------|----------------------------------------------|--|--|

| mode = 26%      | sampling mode = $74\%$            |                                              |  |  |

| % in            | % in                              | % in                                         |  |  |

| Non-Seizure     | Seizure                           | Non-Seizure                                  |  |  |

| 16%             | 40%                               | 60%                                          |  |  |

|                 | mode = 26%<br>% in<br>Non-Seizure | mode = 26%sampling% in% inNon-SeizureSeizure |  |  |

It should be pointed out that the dynamic thresholding technique does not imply seizure detection is an inherent feature of the system. Due to patient-to-patient variations as well as temporal variations, seizure detection is a complicated task often requiring complex data-driven algorithms [59][60]. In the presented system, the suggested technique is capable of determining high-activity events that could be an artifact, noise, interference, or a seizure, and adjusting

resolution of the system accordingly. Seizures are only selected as a show case for neurologicallyrelevant events.

Lastly, in order to evaluate the power efficiency of this technique, the system was tested for a total of 16 EEG epochs, each containing high activity seizures. To obtain a power efficiency factor for the saved power in wireless transmission, power consumption was calculated for two scenarios of with and without the proposed adaptive resolution.

By calculating the total power consumed for each scenario, it can be seen that power consumption in the transmitter will be nearly halved in the second scenario. The overall power efficiency factor for the tested epochs was calculated as,

$$\eta = \frac{\text{Total power without adaptive resolution}}{\text{Total power with adaptive resolution}} = \frac{17 \times 10^{-6}}{9.75 \times 10^{-6}} = 1.74$$

(2.12)

This is equivalent to an average 43% energy reduction. It must be pointed out that this number could be even higher by (a) reducing the "low resolution" number of bits to 3 or 2, (b) by using more than two levels of resolution, (c) by adjusting the threshold values to make them less sensitive to high-activity episodes.

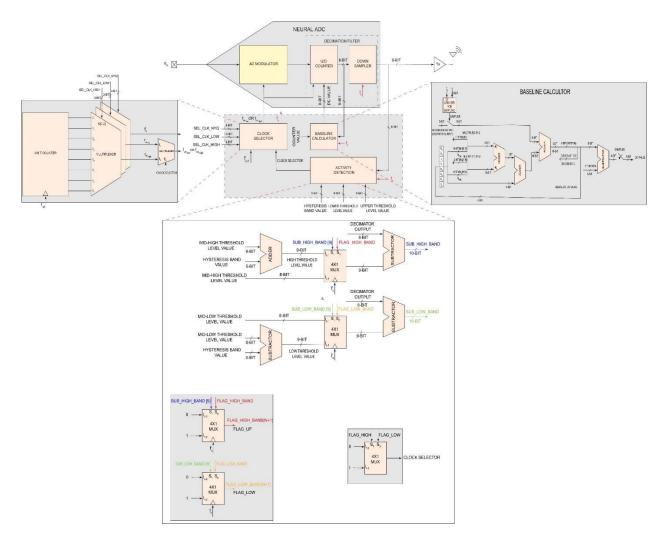

# Chapter 3 Digital Back-End On-Chip Implementation

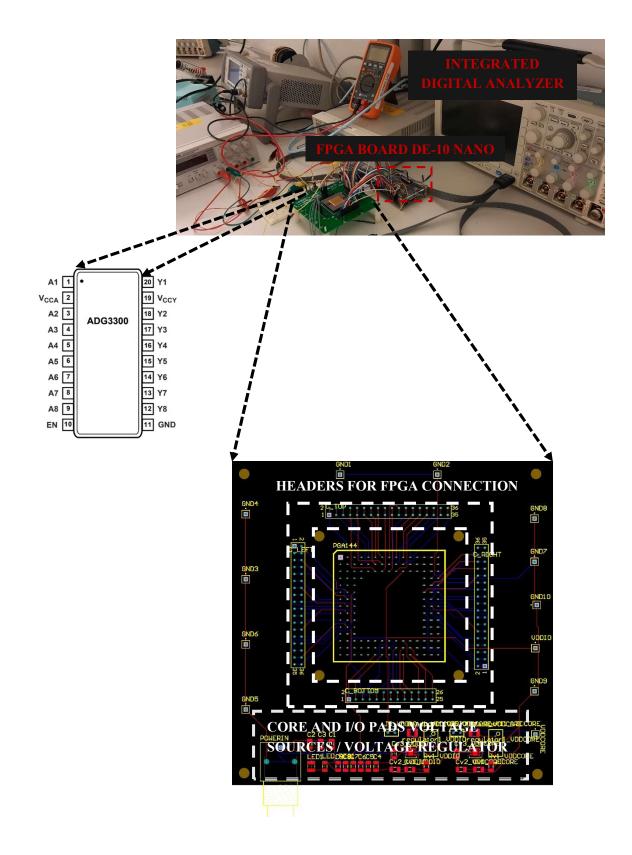

In the previous chapter, a behavioural system-level implementation of the proposed adaptiveresolution recording channel was described. In this chapter, we will discuss the hardware implementation of the digital back-end, the physical implementation of the design in a standard CMOS sub-micron process, and the developed testbench and measurement setup for the fabricated chip. The digital blocks in this system were first implemented in register transfer level (RTL) using Verilog hardware description language (HDL). Next, using Synopsys Design Compiler [36], they

Figure 3.1 Top-level block diagram of the proposed recording channel and the detailed implementation of the digital blocks.

were synthesized and optimized for gate-level implementation, and then were implemented and verified in layout-level using Cadence Innovus, NC-Verilog tools, and eventually entire design was physically verified and signed-off using Cadence Virtuoso tools. In the following sections, the implementation of each of these blocks is described and their simulation results are shown.

### 3.1 Block-level Implementation

Figure 3.1 depicts the top-level block diagram of in the proposed recording channel as well as the mixed-signal front-end (i.e., the modulator shown in yellow) and the digital back-end (blocks shown in blue). Except for the  $\Delta\Sigma$  modulator, all other blocks in this figure are fully digital and are implemented using TSMC 130nm standard CMOS digital cells and with the aid of the kit-associated CAD tools.

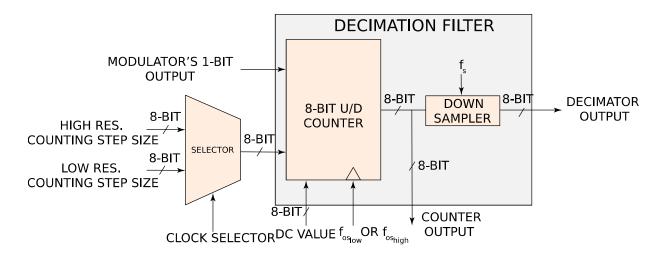

### 3.1.1 Decimation filter

Figure 3.2 shows the internal block diagram of the decimation filter, which is implemented using an 8-bit U/D counter that its output is down sampled to Nyquist-rate frequency ( $f_s$ ). The output of the  $\Delta\Sigma$  modulator which is a 1-bit digital signal is fed to the counter to set the direction of counting (up or down). Also the step size of the counter is set by one of the two control signals selected according to the modulator's clock frequency.

As discussed in chapter 2, in order to reconstruct the input signal through the feedback path of the mixed-signal modulator, an appropriate voltage step size needs to be chosen (the details of the mixed signal front-end implementation is discussed in the next chapter). The voltage step size is chosen according to the desired signal-to-noise ratio (SNR). To reconstruct the signal with two different resolutions in the decimator, the counter's counting step size needs to be set proportional to the voltage step size to achieve correct resolutions.

As an example, for 8 and 4-bit resolutions, if the voltage reference sizes are chosen as  $20\mu V$  and 80  $\mu V$ , the "HIGH RES. COUNTING STEP SIZE" and "LOW RES. COUNTING STEP SIZE" values in Figure 3.2, need to be set as 8'b00000001 and 8'b00000100, respectively. This means that for the high resolution, that is 8-bit, counter changes its value by the smaller step size, and for the low resolution, counter's step size is 4 times larger ( $\frac{80 \ \mu V}{20 \ \mu V} = 4$ ). Later during wireless data transmission, for high resolution sampled data, all 8 bits are sent, and for the low resolution case, only 6 bits are needed to be sent as the two LSBs' value never change. In addition, since the low-resolution mode has 4 bits of accuracy in this example, only 4 bits of the remaining 6 bits

Figure 3.2 Internal block diagram of variable-rate of decimation filter

contain meaningful information, and the two MSBs do not change when operating in lowresolution mode, hence, they will not be transmitted either.

The reduction in the number of bits, as explained in previous chapter, will result in saving power during transmission. It should also be noted that by setting a flag at the beginning of the resolution's change, the receiver will recognize whether the packages are 4-bit or 8-bit information. An automatically adjustable DC value is another input of the decimation filter in Figure 3.2. This input which comes from the baseline calculator unit, is constantly subtracted from the counter's value to always set the reconstructed amplitude at a relatively-fixed DC level.

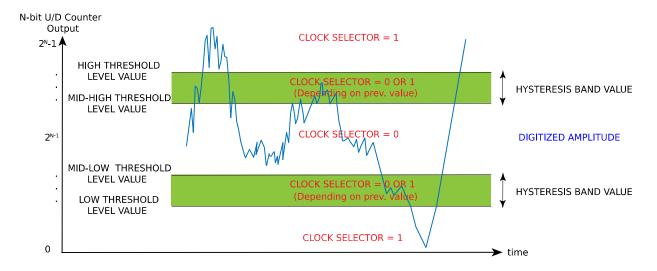

### 3.1.2 Activity detection unit

Figure 3.3 shows the operation principle of the activity detection unit and the generated outputs of this unit based on signal's activity. The blue waveform represents the incoming digitized data from the output of the decimator. To determine the level of the activity of the signal, a set of thresholds are defined. The threshold levels as well as the size of hysteresis band are designed to be adjustable. The outcome of the thresholding process is "CLOCK SELECTOR". If signal's

Figure 3.3 Threshold levels and "CLOCK SLECTOR" flag value versus signal magnitude variations.

magnitude becomes higher than the highest threshold level (i.e. "HIGH THRESHOLD LEVEL") or lower than the lowest threshold level (i.e. "LOW THRESHOLD LEVEL"), signal is determined to have high activity, and therefore the "CLOCK SELECTOR" flag will be set to 1 which will change the system's clock frequency to the high oversampling rate ( $f_{OS_{hig}}$ ), resulting in high-resolution quantization. Similarly, if the signal's amplitude falls between "MID-HIGH THRESHOLD LEVEL" and "MID-LOW THRESHOLD LEVEL" threshold levels, signal is determined to have low activity, resulting in "CLOCK SELECTOR" to be 0, and consequently, operating with  $f_{OS_{tow}}$  that leads to low-resolution quantization. The hysteresis bands which are the green areas in Figure 3.3, are meant to prevent unwanted oversampling frequency changes for when the signal has very-short-time jumps in its amplitude which don't really indicate activity change. When signal is in the hysteresis band regions, the "CLOCK SELECTOR" flag will be maintaining its value.

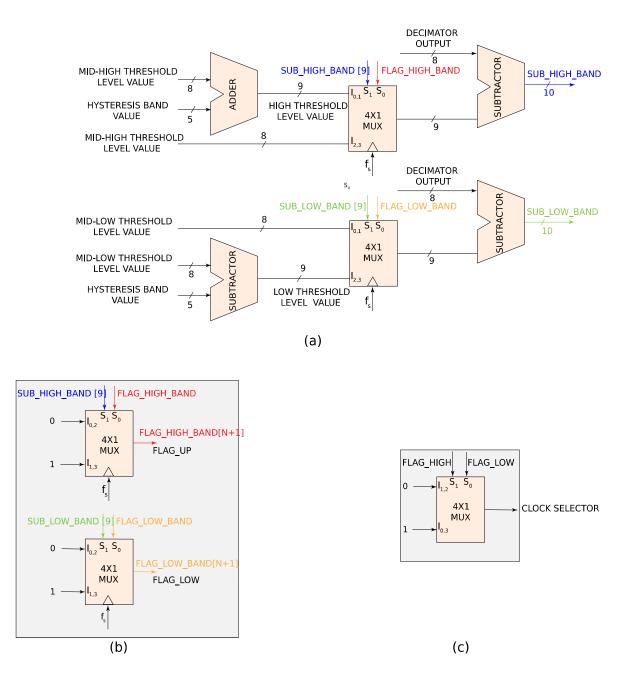

Figure 3.4 shows the internal block diagram of the activity detection unit. The main inputs of this unit are the two threshold levels and the hysteresis band value, all adjustable by the user.