# GENERIC ON-BOARD-COMPUTER HARDWARE AND SOFTWARE DEVELOPMENT FOR NANOSATELLITE APPLICATIONS

### KONSTANTIN BORSCHIOV

A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER'S OF SCIENCE

GRADUATE PROGRAM IN EARTH AND SPACE SCIENCE YORK UNIVERSITY TORONTO, ONTARIO

NOVEMBER 2012

# GENERIC ON-BOARD-COMPUTER HARDWARE AND SOFTWARE DEVELOPMENT FOR NANOSATELLITE APPLICATIONS

### by Konstantin Borschiov

A thesis submitted to the Faculty of Graduate Studies of York University in partial fulfilment of the requirements for the degree of

#### MASTER OF SCIENCE

### © 2012

Permission has been granted to: a) YORK UNIVERSITY LIBRARIES to lend or sell copies of this thesis in paper, microform or electronic formats, and b) LIBRARY AND ARCHIVES CANADA to reproduce, lend, distribute or sell copies of this thesis anywhere in the world in microform, paper or electronic formats *and* to authorize and procure the reproduction, loan, distribution or sale of copies of this thesis anywhere in the world in microform, paper or electronic formats.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

### GENERIC ON-BOARD-COMPUTER HARDWARE AND SOFTWARE DEVELOPMENT FOR NANOSATELLITE APPLICATIONS

### by Konstantin Borschiov

By virtue of submitting this document electronically, the author certifies that this is a true electronic equivalent of the copy of the thesis approved by York University for the award of the degree. No alteration of the content has occurred and if there are any minor variations in formatting, they are as a result of the conversion to Adobe Acrobat format (or similar software application).

**Examination Committee members:**

- 1. Dr. Regina Lee

- 2. Dr. Michael Daly

- 3. Dr. Brendan Quine

- 4. Dr. George Vukovich

### **Abstract**

This study outlines the results obtained from the development of a generic nanosatellite on-board-computer (OBC). The nanosatellite OBC is a non-mission specific design and as such it must be adaptable to changing mission requirements in order to be suitable for varying nanosatellite missions. Focus is placed on the commercial-off-the-shelf (COTS) principle where commercial components are used and evaluated for their potential performance in nanosatellite applications. The OBC design is prototyped and subjected to tests to evaluate its performance and its feasibility to survive in space.

### **Acknowledgements**

I would like to thank all those who have supported me and encouraged my work through my years at York University. In particular I would like to thank my supervisor, Professor Regina Lee, for her continued support and motivation as I have progressed with my research.

I would like to thank the entire YuSEND team at York University, both past and present members, for their friendship, continued motivation and willingness to assist me whenever I have come across problems. In particular, Mark Post, whose knowledge of electronics and software has proved most invaluable as my research has progressed. I would also like to acknowledge Hugh Chesser for keeping the group on track and making us always think of the big picture. I would like to thank Anthony Dineen for providing with very needed distractions to the otherwise stressful days.

I would also like to express my gratitude to Professor Brendan Quine for his assistance and support during the TVAC testing stage.

I would like to thank COM DEV and the Natural Science and Engineering Council for their financial support.

I would like to express my gratitude and thanks to Beth Duffus for keeping me in line and on track as I was working towards the completion of my work and the writing of my thesis. Lastly, I want to thank my parents whose patience and support during my entire life has brought me to where I am today.

# **Table of Contents**

| Abstract  |                                                         | iv  |

|-----------|---------------------------------------------------------|-----|

| Acknow    | ledgements                                              | v   |

| Table of  | Contents                                                | vi  |

| List of F | igures                                                  | ix  |

| List of T | ables                                                   | xi  |

| List of A | Acronyms                                                | xii |

| Chapter   | 1 - Introduction                                        | 1   |

| 1.1.      | Space Environment and Its Effects on Computer Systems   | 7   |

| 1.2.      | Historical Overview                                     | 9   |

| 1.2.      | 1. Previous Nanosatellite Computer Hardware Development | 10  |

| 1.2.      | 2. Previous Nanosatellite Software Development          | 12  |

| 1.3.      | Thesis Statement and Contribution                       | 12  |

| 1.4.      | Outline                                                 | 14  |

| Chapter   | 2 – Hardware Design                                     | 15  |

| 2.1.      | Hardware Constraints                                    | 15  |

| 2.2.      | Available Embedded Computer Systems                     | 18  |

| 2.3.      | Component selection                                     | 21  |

| 2.3     | .1. Processor         |                           | 22 |

|---------|-----------------------|---------------------------|----|

| 2.3     | .2. Memory            |                           | 26 |

| 2.3     | 3.3. Voltage Regula   | ator                      | 33 |

| 2.3     | 4.4. Passive Compo    | onents                    | 37 |

| 2.4.    | Design Layout         |                           | 43 |

| 2.5.    | Complete Design of    | f the On Board Computer   | 51 |

| 2.6.    | Cost Analysis of Pro  | esent OBC Design Hardware | 52 |

| 2.7.    | Expected Power Co     | onsumption                | 54 |

| Chapter | r 3 – Software        |                           | 56 |

| 3.1.    | Trade-Off Study on    | Types of Software         | 56 |

| 3.2.    | Trade-Off Study of    | Open Source Software      | 58 |

| 3.3.    | OBC Boot Process.     |                           | 58 |

| 3.4.    | Required Software     | Components                | 61 |

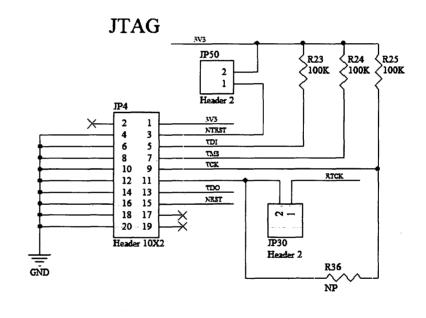

| 3.5.    | JTAG Interface        |                           | 62 |

| 3.6.    | MRAM Driver           |                           | 63 |

| 3.7.    | XENOMAI Real Ti       | ime Framework             | 64 |

| 3.8.    | OBC Filesystem        |                           | 65 |

| 3.9.    | Triple Modular Red    | lundancy                  | 67 |

| Chapter | r 4 – Assembled Syste | em Performance Evaluation | 72 |

| 4.1. Power Consumption of OBC       |

|-------------------------------------|

| 4.2. General Performance Evaluation |

| 4.3. Thermal Cycling Test           |

| 4.4. Thermal Vacuum Test            |

| 4.4.1. Thermocouples                |

| 4.4.2. Test Setup                   |

| Chapter 5 – Final Remarks           |

| References 92                       |

| Appendix A – OBC Schematics         |

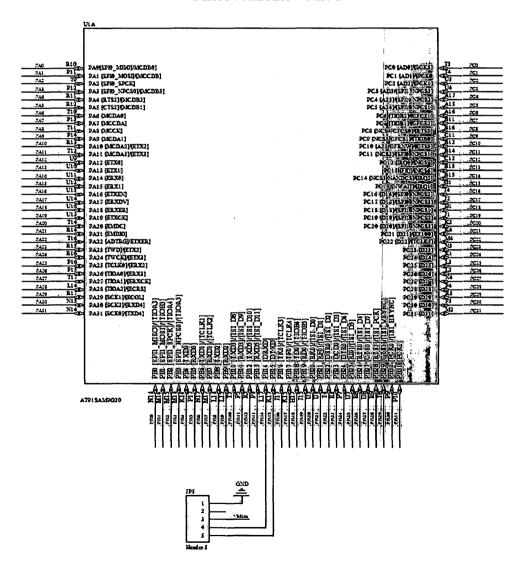

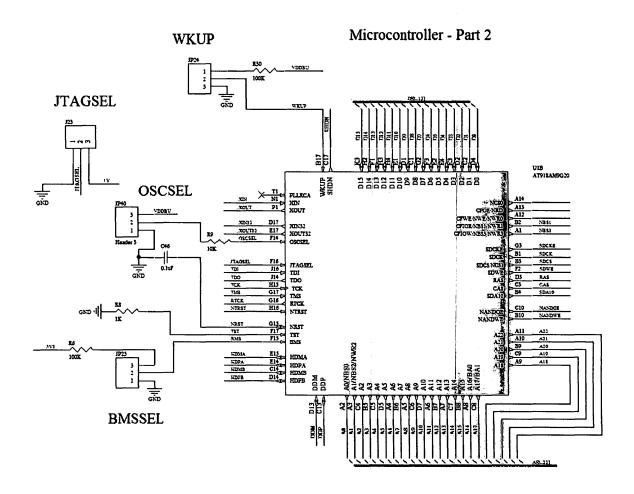

| A. Microcontroller – AT91SAM9G20    |

| B. Power Regulator Schematic        |

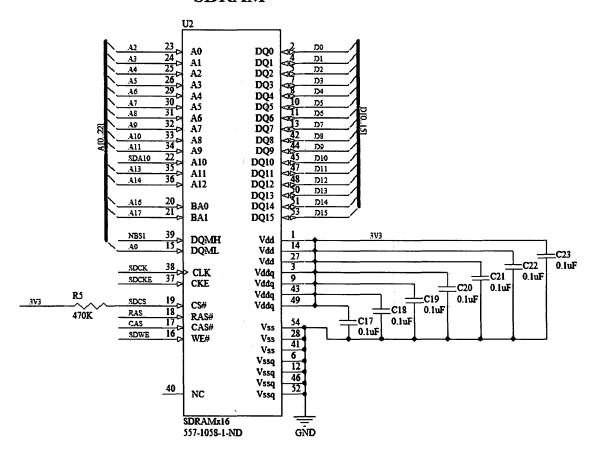

| C. SDRAM Schematic 10               |

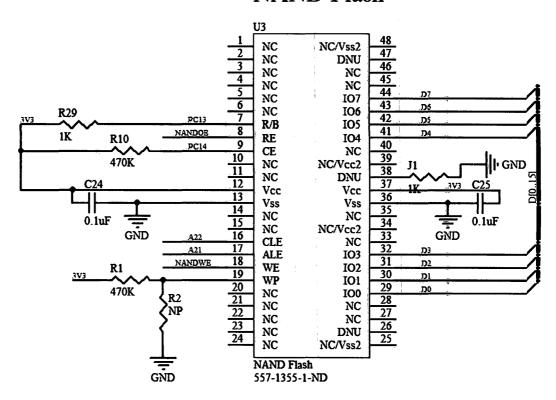

| D. NAND Flash Schematic 103         |

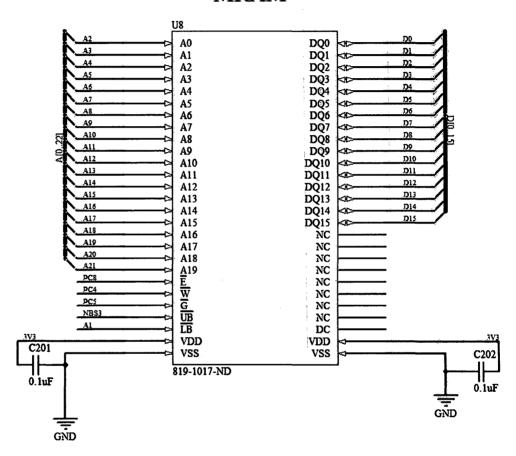

| E. MRAM Schematic                   |

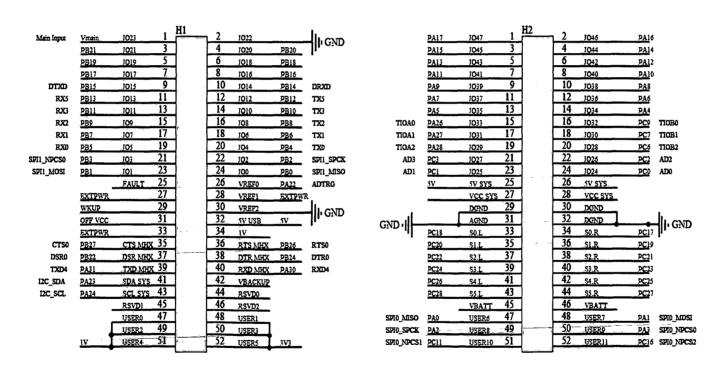

| F. Headers Schematic                |

| Appendix B – TMR Sample Code        |

# **List of Figures**

| Figure 1 - 1U CubeSat Model Developed at York University                       | 2       |

|--------------------------------------------------------------------------------|---------|

| Figure 2 – Poly-Picosatellite Orbital Deployer (P-POD) Model and Cross Section | Image   |

| Credit: Cal Poly [2]                                                           | 3       |

| Figure 3 - Common Nanosatellite Configuration                                  | 4       |

| Figure 4 - PC/104 Plus Board with Headers Source Image: PC/104 Plus Specifi    | cations |

| [17]                                                                           | 17      |

| Figure 5 - Modified PC/104 Form Factor                                         | 17      |

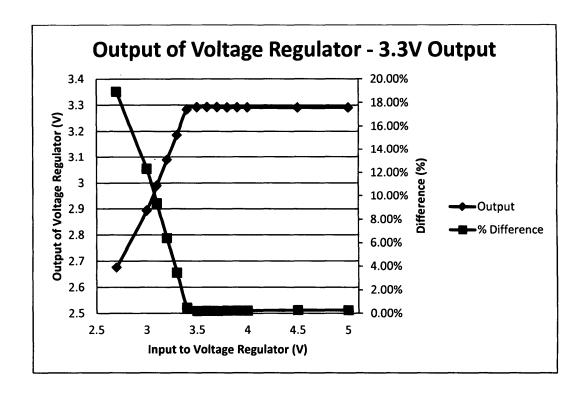

| Figure 6 - Output of Voltage Regulator, 3.3V                                   | 36      |

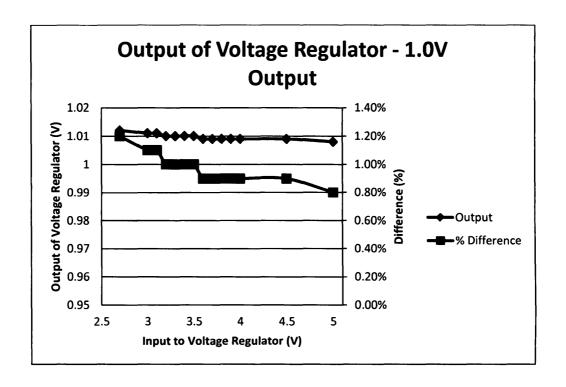

| Figure 7 - Output of Voltage Regulator, 1.0V                                   | 37      |

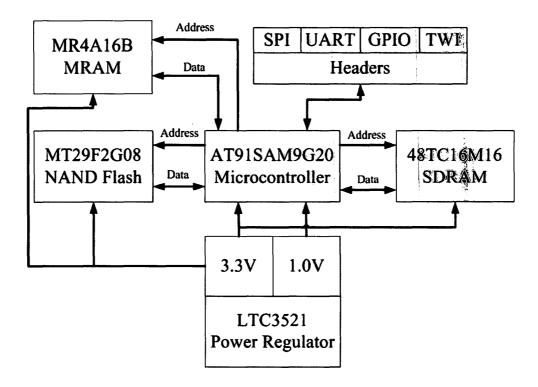

| Figure 8 - Hardware Block Diagram                                              | 44      |

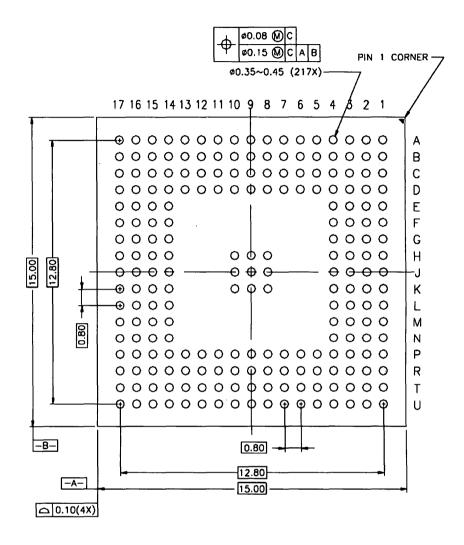

| Figure 9 - Bottom view of AT91SAM9G20, dimensions are in mm [27]               | 46      |

| Figure 10 - Close up view of BGA microcontroller solder pads                   | 47      |

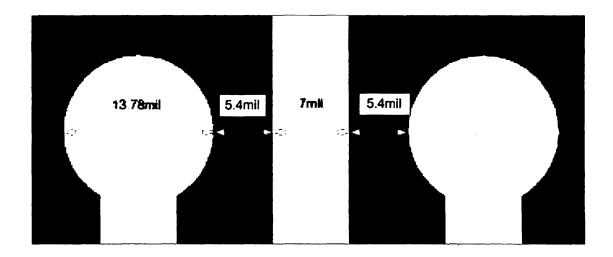

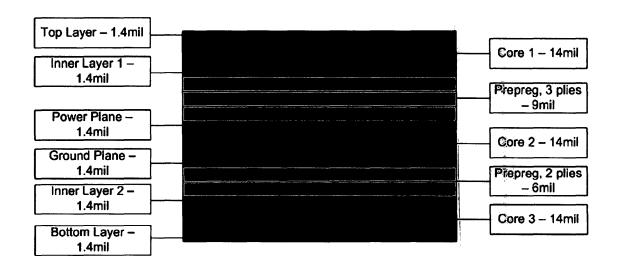

| Figure 11 - OBC Board Stackup                                                  | 48      |

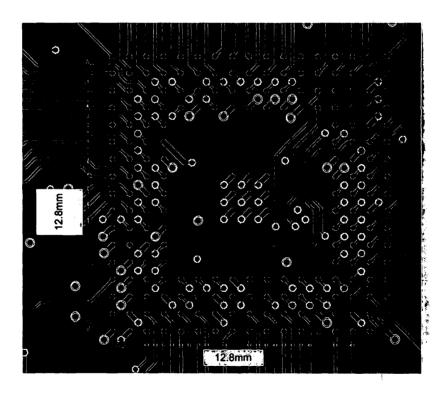

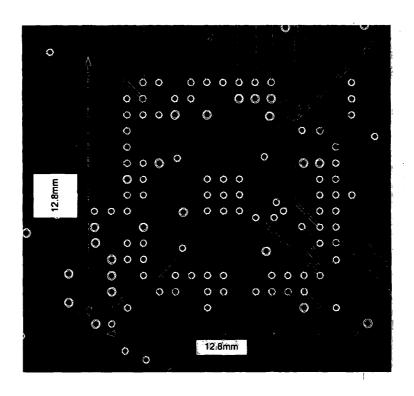

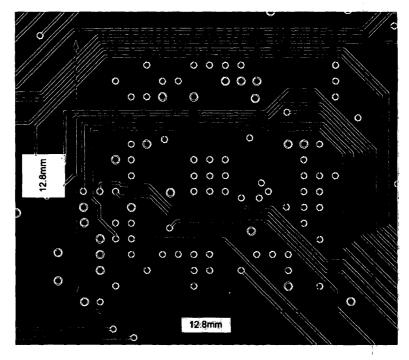

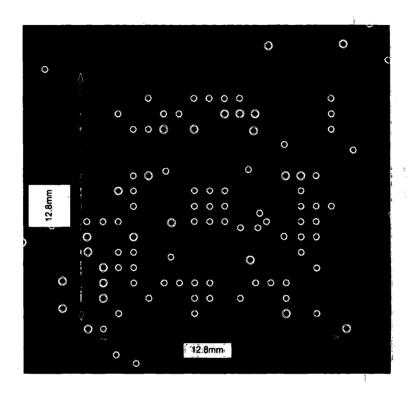

| Figure 12 - Top Layer Fan-Out of Microcontroller Connections                   | 49      |

| Figure 13 - First Inner Layer Fan-Out of Microcontroller Connections           | 50      |

| Figure 14 - Second Inner Layer Fan-Out of Microcontroller Connections          | 50      |

| Figure 15 - Bottom Layer Fan-Out of Microcontroller Connections                | 51      |

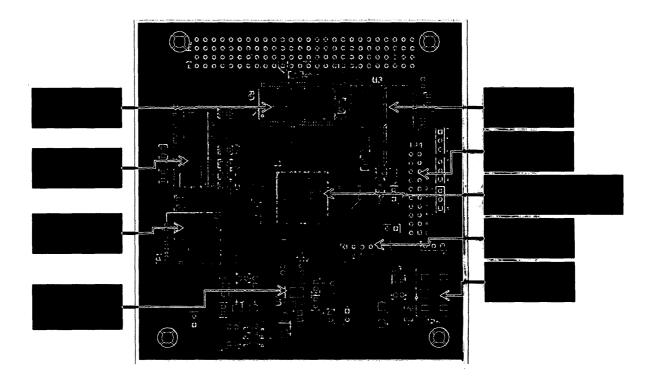

| Figure 16 - Final Layout of OBC                                                | 52      |

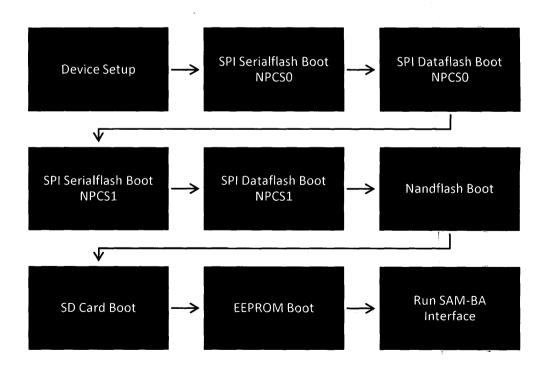

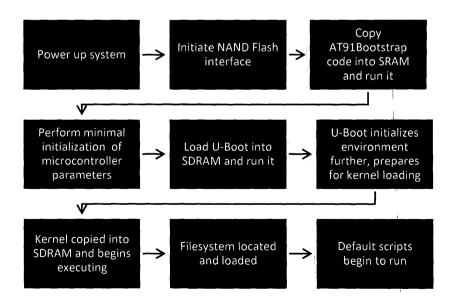

| Figure 17 - Microcontroller Boot Process. Adapted from datasheet [27]          | 59      |

| Figure 18 - Boot Process of Present OBC Design                                 | 60      |

| Figure 19 - Unmodified AT91Bootstrap Binary Data                             | 69  |

|------------------------------------------------------------------------------|-----|

| Figure 20 - Modified AT91Bootstrap Binary Data                               | 70  |

| Figure 21 - Present OBC Design in Thermal Chamber                            | 77  |

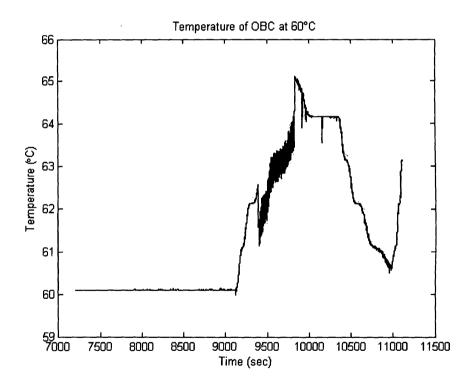

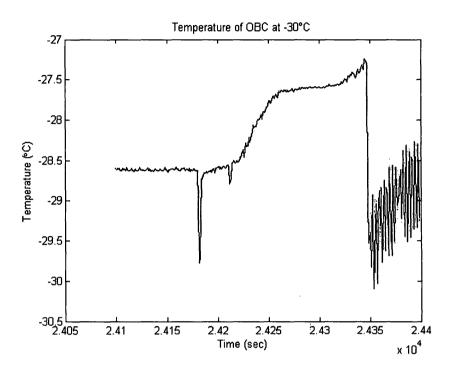

| Figure 22 - OBC Operational Temperature at 60°C                              | 78  |

| Figure 23 - OBC Operational Temperature at -30°C                             | 79  |

| Figure 24 - Layering of Thermocouple Attachment                              | 81  |

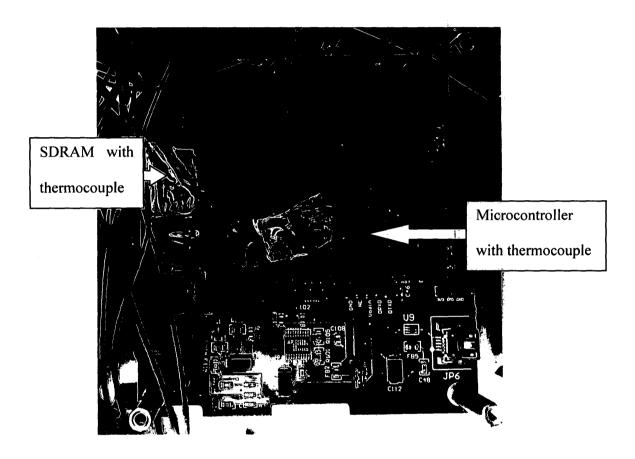

| Figure 25 - OBC in TVAC with Thermocouples Attached                          | 82  |

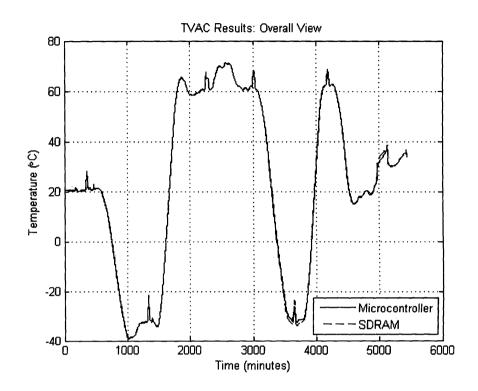

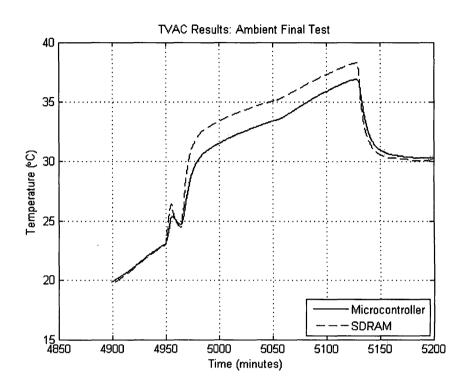

| Figure 26 - Temperature of OBC Microcontroller and SDRAM throughout the Test | 85  |

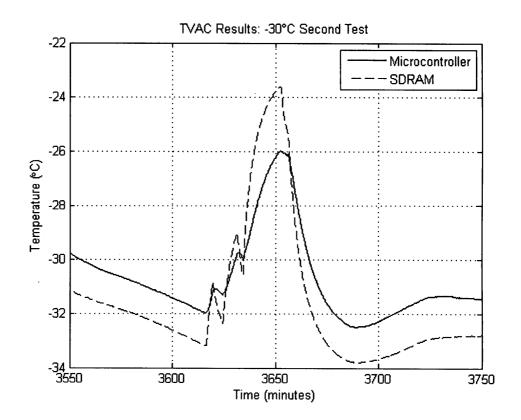

| Figure 27 - Second -30°C Test                                                | 86  |

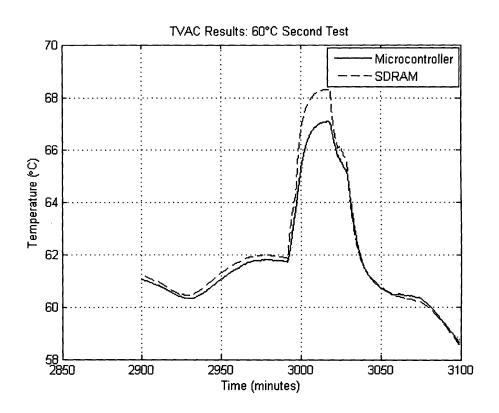

| Figure 28 - Second 60°C Test                                                 | 87  |

| Figure 29 - Final Test at Ambient Temperature                                | 88  |

| Figure 30 - Microcontroller Schematic - Part 1                               | 102 |

| Figure 31 - Microcontroller Schematic - Part 2                               | 103 |

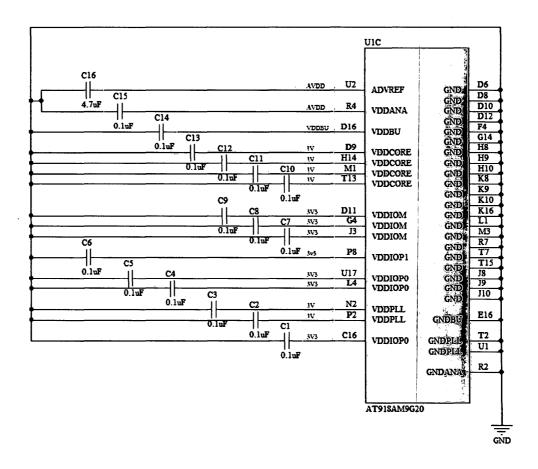

| Figure 32 - Microcontroller Schematic - Part 3                               | 104 |

| Figure 33 - Microcontroller Schematic - Part 4                               | 105 |

| Figure 34 - Power Regulator Schematic                                        | 106 |

| Figure 35 - SDRAM Schematic                                                  | 107 |

| Figure 36 - Nand Flash Schematic                                             | 108 |

| Figure 37 - MRAM Schematic                                                   | 109 |

| Figure 38 - Headers Schematic                                                | 110 |

# **List of Tables**

| Table 1: Summary of Commercial Embedded Systems           | 20 |

|-----------------------------------------------------------|----|

| Table 2: Comparison of Non-Volatile Memories              | 28 |

| Table 3: Comparison of Flash operations                   | 29 |

| Table 4: Specifications of Chosen SDRAM [35]              | 31 |

| Table 5: Comparison of MRAM Products                      | 33 |

| Table 6: Operational Voltage Levels of Active Components  | 34 |

| Table 7: Resistor Technologies                            | 39 |

| Table 8: Capacitor Technologies                           | 41 |

| Table 9: Cost Breakdown of OBC Components <sup>1</sup>    | 53 |

| Table 10: Theoretical Power Consumption of OBC Components | 55 |

| Table 11: Measured Power Consumption of OBC               | 72 |

| Table 12: Benchmark Tests of Embedded Systems             | 74 |

## **List of Acronyms**

AC Alternating Current

ADC Analog-to-Digital Converter

API Application Programming Interface

ARM Advanced RISC Machine

ASIC Application Specific Integrated Circuits

BGA Ball Grid Array

CANOE Canadian Advance Nanosatellite Operating Environment

COTS Commercial Off The Shelf

DDR Double Data Rate

DRAM Dynamic Random Access Memory

EDAC Error Detection and Correction

EEPROM Electrically Erasable Programmable Read Only Memory

ENIAC Electronic Numerical Integrator And Computer

FPGA Field Programmable Gate Array

FRAM Ferroelectric Random Access Memory

GNB Generic Nanosatellite Bus

GPIO General Purpose Input/Output

HDL Hardware Description Language

JFFS2 Journaling Flash File System version 2

JTAG Joint Test Action Group

KiB Kibibyte (1024 bytes)

LEO Low Earth Orbit

MiB MebiByte (1024 KiB)

MRAM Magnetoresistive Random Access Memory

NASA National Aeronautics and Space Administration

OBC On-Board Computer

PCB Printed Circuit Board

P-POD Poly-Picosatellite Orbital Deployer

RISC Reduced Instruction Set Computing

ROM Read Only Memory

SDR Single Data Rate

SDRAM Synchronous Dynamic Random Access Memory

SEE Single Event Effects

SoC System on a Chip

SRAM Static Random Access Memory

TID Total Ionizing Dose

TMR Triple Modular Redudnacy

TVAC Thermal Vacuum

TWI Two Wire Interface

UART Universal Asynchronous Receiver/Transmitter

UBI Unsorted Block Image

UBIFS Unsorted Block Image FileSystem

UTIAS/SFL University of Toronto Institue for Aerospace Studies - Space Flight

Laboratory

YAFFS2 Yet Another Flash File System version 2

YuSEND York University Space Engineering Nanosatellite Demonstration

### **Chapter 1 - Introduction**

The purpose of the research is to develop a nanosatellite on-board-computer (OBC) for generic nanosatellite missions. The OBC design takes into account limitations of nanosatellites and the environment they operate in.

A nanosatellite is a sub-classification of satellite types by mass. Several range definitions for nanosatellites exist but the one that is being used in this thesis is the range of 1kg to 10kg. Definitions of the mass range can vary from different countries to different institutions. In Canada the accepted definition is the one mentioned above [1] while the CubeSat standard defines that range as a picosatellite [2].

Nanosatellites are becoming increasingly popular due to being small enough that they are launched for less cost than a traditional large satellite. In order to accomplish useful tasks, nanosatellites tend to focus on using commercial-off-the-shelf (COTS) products in order to drive cost down further [1]. Advances in electronics also mean that commercial electronics are more powerful and smaller in comparison to older technology even as recent as 10 years ago and they allow nanosatellites to be capable of accomplishing tasks that in the past required a larger satellite.

Since the nanosatellite subcategory only defines the mass of the satellite, it is often left to the designers to choose other parameters. A class of nanosatellites known as CubeSat refers to a specific set of physical parameters of nanosatellites including shape and tolerances. CubeSat specifications define three categories of satellite where the smallest one is a cube with dimensions of 10x10x13.5 cm<sup>3</sup> and a mass limit of 1.33kg [2], known

as a 1U CubeSat, where the U stands for unit. Figure 1 below depicts a 1U CubeSat under development at York University.

Figure 1 - 1U CubeSat Model Developed at York University

The specifications define the largest CubeSat as being a 3U CubeSat with dimensions  $10x10x34.5 \text{ cm}^3$ . The specifications are an attempt at creating a standardized form factor such that multiple nanosatellites can be loaded onto a single launcher known as a Poly Picosatellite Orbital Deployer (P-POD) [3]. Note that the CubeSat specifications use the picosatellite designation for the CubeSat as opposed to the nanosatellite designation as mentioned above. The P-POD is a container into which CubeSats are loaded while it in turn is mounted onto a launch vehicle. The P-POD can accommodate three 1U CubeSats or a single 3U CubeSat inside of it. The use of a P-POD and hence the CubeSat standard, eliminates the need for satellite designers to be concerned about the mounting of the satellite in the launch vehicle. Instead, this is a concern for the designers of the P-POD, of which commercial solutions are available which outline the requirements for how the nanosatellites fit in the commercial P-POD.

Figure 2 – Poly-Picosatellite Orbital Deployer (P-POD) Model and Cross Section Image Credit: Cal Poly [2]

Adherence to CubeSat specifications will help the final product to be compatible with other systems on the market, e.g. a team can design a 1U CubeSat and use a commercial P-POD while possibly sharing launch costs with other nanosatellites designers that want their satellite to be in the same P-POD.

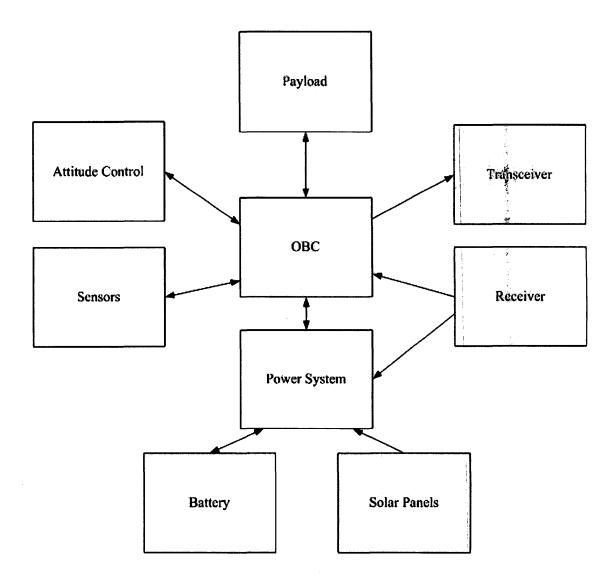

A computer system is central to traditional nanosatellite designs; it provides the capability to perform processing of data as well as control of autonomous tasks. The OBC is connected to the subsystems of a nanosatellite and provides a centralized onboard control center as is shown in Figure 3. A connection between the receiver and the power system exists so that the power system may be able to power cycle the OBC in case of an emergency on command.

Figure 3 - Common Nanosatellite Configuration

Computers in the past used to be large and occupy whole rooms such as the Electronic Numerical Integrator And Computer (ENIAC) which was built in 1946 [4] for the purpose of computing firing tables and was used for other intensive computations as well. The ENIAC used vacuum tubes, which were used to control flow of electric current. The first major step to miniaturization came with the creation of transistors which could replace vacuum tubes and were smaller in size. Initial transistors were used in circuits as

discrete components. Development continued and integrated circuits were created which allowed the formation of large circuits incorporating transistors as well as other electronic components in a discrete package.

A modern computer can be broken down into two fundamental functional blocks: memory and a central processing unit [5]. The memory of a computer is used to store data and commands. Relevant information can be read from the memory and depending on the type of memory, information can be written to it. The central processing unit performs mathematical computations and is able to access the memory to retrieve information to process. The arrangement of the fundamental functional blocks, their connectivity and the resources arrangement is referred to as the computer architecture.

There are two main design architectures for a satellite regarding its OBC design. The first design involves a centralized architecture where the OBC acts as the main processing system and all data collected is passed on to the OBC to perform the necessary work. The second design, also referred to as a distributed architecture, involves subsystems that are able to perform their own processing and pass on the results to the OBC. The OBC in this case plays a more managerial role where it can relay data between subsystems and send data requests to the subsystems.

The centralized architecture is more common for simpler systems where subsystems can wait for the OBC to finish processing previous data. The subsystems can also share the OBC's processing power to work on several tasks using a scheduler and time allocation techniques. Such an approach may be necessary due to lack of space or power to support additional computing devices.

The distributed architecture is appropriate for systems where there is a large amount of data to be processed and subsystems are operating continuously. This is used to reduce the workload on the OBC and allows faster operation of the system as a whole. This approach is more appropriate for nanosatellite design as it contains several critical subsystems (e.g. power, communication), often as separate modules, which may require real time processing and collection of data continuously.

A hybrid approach is also possible where critical subsystems will have their own processing power while others will rely on the OBC to perform the necessary tasks.

The generic nature of the proposed OBC design allows it to be implemented within a larger system using any of the above approaches; although for a nanosatellite, the distributed or hybrid architectures are preferred.

The OBC design developed as part of the research can be configured for either design option. Such configurations are investigated on a mission specific basis and begin through identification of systems and whether processing power can be shared with other systems.

It is desired for the developed OBC to possess real time capabilities. Real time when referring to computer systems means that there are set time limits as to when a task must be accomplished by. A generic non real time system such as a desktop computer is designed to improve average time response. This does not prevent a task from waiting a long time before it is able to complete. A system with real time capabilities is designed to set and attempt to reduce the maximum time that a task may require to complete. Real time systems may be divided into two categories: soft real time and hard real time [6].

Soft real time systems guarantees that real time tasks will receive priority for execution but there is no guarantee that they will meet their timing constraints. Hard real time systems must guarantee that tasks meet their timing constraints and failure to do so produces a critical error.

### 1.1. Space Environment and Its Effects on Computer Systems

The present OBC design is intended for use aboard a nanosatellite and as such it is subject to the effects of the space environment. The space environment that affects the present OBC design includes vacuum, temperature extremes and radiation, each of which presents a challenge in the design of the system.

When a satellite is launched into space it is typically placed into a low Earth orbit (LEO) with various configurations as per mission requirements. The low Earth orbit range is generally accepted to be up to an altitude of 2000 km above sea level [7]. At these altitudes in typical nanosatellite missions, the atmospheric pressure and density are very low and the condition is considered a 'vacuum'. The vacuum is not a perfect vacuum as particles are present at low quantities which vary with altitude.

There are two effects of vacuum that are significant for satellites. Liquids in vacuum evaporate at temperatures well below their boiling temperatures. Liquid filled components that are not hermetically sealed and able to withstand the pressure difference rupture in vacuum. For example, electronic components such as electrolytic capacitors, which are filled with liquid, will rupture and be destroyed under vacuum conditions. Solid components are subject to an effect called outgassing where gasses that are trapped

within are released in vacuum condition. Outgassing materials are detrimental to spacecraft operations as they can attach themselves to parts of the spacecraft, such as solar panels and lenses, and reduce their performance.

The second effect of vacuum on satellites involves the lack of convection. Convection is an effective method of removing heat from a system. In a desktop and laptop computers, convection with the assistance of a fan prevents the system from overheating. Overheating of electronic components beyond their maximum rated temperature is generally destructive.

In low Earth orbit, the lack of an atmosphere causes extreme temperature variations dependent on being in view of the sun. When a satellite in low Earth orbit is hidden from the sun by Earth, the lack of atmosphere causes a rapid cool down due to a lack of energy being absorbed as well as heat energy being dissipated away from the satellite. When in view of the sun, the satellite is not protected by Earth's atmosphere and will be subject to the sun's radiation, raising its temperature. Combined with the lack of convection, an operational satellite may reach extremely high temperatures. The temperatures that a satellite can reach are dependent upon the altitude of the orbit, heat generated by satellite systems as well as time spent in view of the sun. This is important for electronic systems as components are rated to work within a particular temperature range. The operational temperature range of electronic components varies between components and it is a property that must be examined when selecting a device.

Radiation causes both failures and errors in electronics. The majority of radiation in low Earth orbit consists of energetic protons and electrons as well as heavier ions [8] that strike circuits. Electronic components are made out of doped semiconductor materials and when energetic particles strike them, they may cause single event effects (SEEs) and generation of charge within the semiconductor known as total ionizing dose (TID).

The effects of TID and SEEs are varied and may lead to build up of charge, shorting of regions that are normally insulated and switching in state. The results of these effects are memory errors and improper operation of components as well as complete failure.

Electronic components can be produced that are suited for operation in an environment containing radiation such as space. Such components are known as radiation tolerant and radiation hardened components. Radiation hardened devices are capable of operating in a radiation environment up to their defined limits. Radiation tolerant devices are capable of operating in radiation environments if protection schemes are implemented. Such components are more expensive than their equivalent non hardened or tolerant devices.

#### 1.2. Historical Overview

Nanosatellites are an increasingly popular platform for educational institutions to educate their students in the area of satellite and space mission design with tangible results and even the possibility of an actual launch. The Nanosatellite Launch Program which is headed by University of Toronto Institute for Aerospace Studies (UTIAS) has launched several nanosatellites [9] built by universities and organizations from different countries. The advantages of nanosatellites are their lower cost and mission scope, which result in a

short design and construction phase in comparison to that of a larger satellite that can involve several years of development, high priced contractors and equipment, and proprietary development.

### 1.2.1. Previous Nanosatellite Computer Hardware Development

Nanosatellites have been flown from educational, commercial and governmental institutions and each has varying techniques of implementing their OBC. Research from the University of Stellenbosch has outlined the design of an Advanced RISC Machine (ARM) based OBC for nanosatellites [10]. Focus was placed on the type of microcontroller that is used (the AT91SAM7A2 ARM7 based processor) and its functionality in their research. The FPGA used for error detection and correction (EDAC), and on the qualification of the processor for the space environment were also examined in their study.

Research from UTIAS, who have successfully launched several nanosatellites, outlines the top level architecture of the OBC used on the CanX series satellites [11]. While the study focuses mostly on the overall nanosatellite configuration and the software for the on-going missions, it also includes a detailed description of the major components on the OBC. While specific parts are not named in the document, their functionality is described. In [11], it is seen that the OBC is composed of the bare essentials needed including a microcontroller for the processing and execution of software, volatile memory to provide an area for execution of tasks and non-volatile memory to store the necessary data as outlined by the mission and operational requirements. Focus is placed

on EDAC and it is done through the implementation of a triple modular redundancy (TMR) system in hardware by supplying three memory chips that allows the memory controller to use triple voting through a hardware voter.

Another design approach to a satellite OBC is to create a redundant scheme where there are two central units that are capable of working independently from each other. Researchers at the Politecnico di Torino have designed an architecture for a small satellite in which the OBC consists of two processing units which are not identical and can work independently or together [12]. This leads to a design where one faulty component of the OBC may be turned off and the other becomes the main and only processor. This provides an extra layer of protection against a critical fault in the OBC.

A common theme with the aforementioned designs is that they do not specify the use of any radiation hardened equipment as part of the system. Any component that is mentioned in all designs is a generic commercial component. This is a key issue in developing nanosatellites as the avoidance of radiation hardened equipment will result in lower cost of hardware.

In addition to the standard components used in existing nanosatellite OBC designs. The OBC that was developed as part of this research also contains Magnetoresistive Random Access Memory (MRAM), a type of non-volatile memory. MRAM is a promising technology and has been flown on Sprite-Sat as part of the magnetometer subsystem [13]. The magnetometer subsystem was designed by ÅAC Microtec and the satellite was

launched in 2009. The satellite was operating successfully; however, there is no specific information released about the performance of the MRAM component.

### 1.2.2. Previous Nanosatellite Software Development

A functional OBC must accomplish a set of tasks as outlined by mission requirements which may involve computations and data collection and storage. Those tasks are implemented and controlled through software.

Several educational nanosatellite developers have designed custom, low-level software to run their OBCs. The CanX series nanosatellites use custom software designed and written in house where all required functionality was implemented using direct calls to OBC hardware [11][14].

Developing custom software from the ground up requires significant work and therefore most likely results in increased cost and time. A way to reduce the time dedicated to the software aspect is to use an existing operating system that can be adapted to work on the OBC. Several spacecraft have used such commercial solutions. For example, VxWorks is a proprietary real time operating system that has been used on several space missions such as the Deep Impact spacecraft [15].

### 1.3. Thesis Statement and Contribution

This thesis outlines a hardware design of a nanosatellite OBC as well as the necessary software components in order to produce a working OBC subsystem that is suitable for

space missions. While focus is placed on nanosatellite applications, the present OBC design is also suitable to be used on ground applications such as rovers.

The objectives that drive the design are: power consumption, space environment survivability, low cost and standard interfaces. The power consumption of the system if important due to on orbit power availability which is limited to power generation through the use of solar panels. The space environment poses risks to electronics operation because of the temperatures the equipment is subject to as well as limited heat dissipation in space due to lack of convection in a vacuum. Radiation poses further risks as it may interfere with the operation of electronics.

In order for the design to be competitive with other commercial products it must be cost competitive as well as capable of easy integration into a nanosatellite system. Emphasis is placed on using the commercial-off-the-shelf (COTS) principle in order to create a low cost system through the selection of widely available and commonly used components.

The present OBC design is put through benchmark tests to evaluate its performance in comparison to commercial embedded systems. In additions, results from a qualifications test are presented as well to demonstrate the feasibility of using commercial components for the design of space systems.

#### 1.4. Outline

The thesis is divided into 4 main sections. Chapter 1 details background information about the developments done with nanosatellites computers from a hardware and software perspective as well as presenting the main topic of the research.

Chapter 2 outlines several considerations in designing a computer system and describes the rationale behind the selection of the OBC components.

In Chapter 3, the focus shifts towards how the OBC runs and executes the required tasks. The types of software required are outlined and existing solutions are presented. After the options are investigated and the software components are chosen, a discussion is presented regarding how to integrate the software components together as well as the kind of customization that is required in order to make the software operational on the present OBC design.

Chapter 4 presents results from functional tests performed on the system. This includes functional tests that demonstrate the operation of the system as well as qualification tests that examine system operation under extreme conditions.

The final chapter summarizes important concepts and provides a closing discussion of the development of the present OBC design.

### **Chapter 2 – Hardware Design**

The hardware development phase of the present OBC design is presented in detail. Initial stages prior to designing the hardware consist of evaluating constraints imposed on the design and comparison with existing commercial systems. Design of the hardware involves creating electronic schematic development in conjunction with component selection. Changing of a component may lead to changes in electronic schematics as it may change the electrical connections.

The printed circuit board (PCB) layout phase is started after the schematics are completed and involve creating physical connection between electrical components. Care is taken to create an efficient design that takes makes an effort to reduce noise in the system.

### 2.1. Hardware Constraints

The present OBC design is developed for nanosatellites and the design is based on the CubeSat specifications by the California Polytechnic State University. The specifications define 2 form factors which are the 1U CubeSat and 3U CubeSat. The 1U CubeSat dimensions are  $100.0\pm0.1$ mm  $\times$   $100.0\pm0.1$ mm  $\times$   $113.5\pm0.3$ mm [2]. The limitation of the CubeSat standard as of 2012 is that it defines a satellite with a maximum mass of 4kg. A nanosatellite does not have to adhere to the CubeSat specifications in any way and therefore nanosatellites can exist in varying shapes and sizes. An example of such a nanosatellite would be the AISSat-1 which is constructed by UTIAS/SFL for the government of Norway. This nanosatellite adheres to UTIAS/SFL's own standard of the

Generic Nanosatellite Bus (GNB) and it measures 200mm × 200mm × 200mm [16]. The CubeSat standard was chosen as a guideline for the present OBC design due to it being an established standard with international flight heritage and as such it has compatibility with designs that also follow the CubeSat standard. Other nanosatellite designs can also make use of the present OBC design with the additional requirement that extra modifications may be necessary in order to mount and connect the present OBC design within those nanosatellite designs.

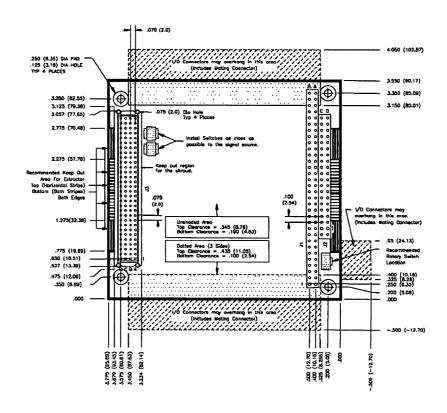

To adhere to the CubeSat standard, the chosen printed circuit board (PCB) form factor is the Pumpkin modified PC/104 Plus standards; PC/104 Plus standards define many aspects of a circuit board including dimensions, mounting holes as well as headers and many other features. Pumpkin Corporation has taken the PC/104 Plus standard and modified the types of headers that are used and have focused on the form factor and mounting holes that the standard defines. The headers that are defined in the PC/104 Plus specifications are shown in Figure 4. For comparison, the header mounting holes of the modified design are shown in Figure 5. The mounting holes at one side of the board in the PC/104 Plus specifications are omitted and the mounting holes on the other side are different, the PCI/104 plus uses PCI compatible headers while the Pumpkin design uses headers with different spacing.

Figure 4 - PC/104 Plus Board with Headers Source Image: PC/104 Plus Specifications [17]

Figure 5 - Modified PC/104 Form Factor

For the present OBC design the Pumpkin PC/104 specifications are used as they are a commercial solution that provides all components necessary for constructing a CubeSat. Pumpkin CubeSat components have an extensive flight heritage [18], being used in over 10 satellites such as QbX1 and Rax. The present OBC design was created such that it is compatible with their equipment so as to provide an alternative to their motherboard that can be integrated with their equipment for use by nanosatellite designers.

The CubeSat and Pumpkin PC/104 specifications are driving guidelines for the present OBC design yet it should be noted that while the CubeSat is the ideal platform for the design, it can be used with other platforms with modification to either the design or the platform itself.

### 2.2. Available Embedded Computer Systems

As part of a trade-off study, several commercial embedded computer systems were examined in order to investigate and compare functionality, power consumption and price of those systems.

Gumstix is a company that sells several types of embedded system modules with varying components and capabilities. To get a complete overview of their system's capability, the specifications of the Overo FE COM system were reviewed as it is one of their top of the line systems with varying functionalities and enhanced operational temperature range. The dimensions of the Overo FE COM are the smallest of all the systems investigated but this comes at a cost where the system has headers at the bottom to allow connection to a daughter expansion board which then increase the size of the system, such boards can be

purchased from Gumstix or produced in house as the actual header connections are disclosed. The actual board design schematics are proprietary information [19].

Linuxstamp II is an embedded system designed and produced by The Linuxstamp Shop, owned and operated by Paul Thomas. The first iteration of the board was previously used at York University for the development of a micro-rover system for a Mars missions as well as by group of engineering students as part of their coursework project relating to nanosatellite communication systems. An advantage of this system is that the board schematics and layout are available to the public as it is an open hardware design [20] and the design can thus be modified as necessary.

The third embedded system that was examined is the LN2440SBC by LittleChips. This is a comprehensive system that includes many peripherals and board schematics are available with purchase of the board [21].

The final commercial embedded system that was investigated is the motherboard from Pumpkin Corporation. This system has the advantage that it is designed for nanosatellites and was designed with a large temperature range and low power consumption to accommodate the constraints of operating in the space environment. The motherboard does not have a processor by default and several options are sold separately by the company that are compatible with the motherboard. A summary of the different characteristics of the above systems are listed in Table 1.

**Table 1: Summary of Commercial Embedded Systems**

|                        | Overo FE COM<br>(Gumstix)                                            | Linuxstamp II<br>(Thomas, 2010)                        | LN2440SBC<br>(LittleChips,<br>2008)                    | CubeSat Kit Flight<br>Motherboard (Not<br>including processor)  |

|------------------------|----------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|

| Price                  | \$229.00                                                             | \$120.00                                               | \$399.00                                               | \$1,200.00                                                      |

| Processor              | Texas Instruments<br>OMAP3530                                        | Atmel<br>AT91SAM9260                                   | Samsung<br>S3C2440A                                    | Varies (socket<br>accommodates<br>several processor<br>modules) |

| Instruction Set        | ARMv7-A                                                              | ARMv5TEJ                                               | ARMv4T                                                 | Varies                                                          |

| CPU                    | ARM Cortex-A8                                                        | ARM926EJ-S                                             | ARM920T                                                | Varies                                                          |

| Clock                  | 600MHz                                                               | 180MHz                                                 | 400MHz                                                 | Varies                                                          |

| Temperature<br>Range   | -40°C - 85°C <sup>2</sup>                                            | Unknown                                                | Unknown                                                | -40°C - 85°C                                                    |

|                        | 256MiB RAM                                                           | 32MiB RAM                                              | 64MiB RAM                                              | On separate processor module                                    |

| Memory                 | 256MiB Flash                                                         | 256MiB Flash                                           | 32MiB Flash                                            | On separate processor module                                    |

|                        | SD Card                                                              | SD Card                                                | -<br>-                                                 | SD Card                                                         |

| Connectivity to System | Custom or prebuilt expansion board                                   | Custom or prebuilt expansion board                     | Headers                                                | Headers                                                         |

| Interfaces             | Bluetooth, Wi-Fi,<br>USB, SPI, I2C,<br>UART, PWM,<br>GPIO, JTAG, ADC | USB, SPI, I2C,<br>PWM, GPIO,<br>JTAG, ADC,<br>Ethernet | USB, SPI, I2C,<br>PWM, GPIO,<br>JTAG, ADC,<br>Ethernet | USB, SPI, I2C,<br>PWM, GPIO, JTAG,<br>ADC <sup>3</sup>          |

| Design                 | Proprietary                                                          | Open hardware                                          | Proprietary<br>layout                                  | Proprietary                                                     |

| Shipped OE             | Open Embedded                                                        | EmDebian                                               | Linux kernel                                           | Purchased separately                                            |

| Dimensions             | 17mm × 58mm ×<br>4.2mm                                               | 41mm × 72.5mm ×<br>15.3mm <sup>1</sup>                 | 140mm ×<br>78mm                                        | 96 mm × 90.2 mm ×<br>12.5 mm                                    |

Linuxstamp II dimensions were obtained manually with calipers

Exception to Bluetooth, Wi-Fi and SD card modules

All require external processor module

Examining the price ranges of the embedded systems it can be seen that the CubeSat Kit Flight MB is significantly more costly than the others, especially due to the fact that it

also requires a pluggable processor module to be complete, which will set its price even higher.

Knowledge of the processor, instruction set and processor that each embedded system uses is important for writing software and compiling it.

Only the Overo FE COM and the CubeSat Kit Motherboard provide a temperature range at which their systems are able to operate. With the Linuxstamp II being an open hardware design, the bill of materials is publicly available and the temperature ratings of all components can be obtained. Operational temperature range is an important characteristic of a system when considering operation in space. In space the system will be subject to extreme temperature ranges, which are dependent on several factors including but not limited to the satellite orbit. A system with a narrow operational range will require extra care to make sure that the temperature it is subject to is within its allowed limits.

### 2.3. Component selection

A computer system is composed of many types of circuits working in conjunction. Integrated circuits have revolutionized the electronics industry by providing complicated circuits on a single die and thus computers became smaller and more powerful. It is required to select the appropriate components in order to design and construct a functional system. The following sections present a description of the selection of the critical components and their role in the present OBC design.

### 2.3.1. Processor

The function of a digital computer is to perform computations. With the invention of integrated circuits, it is possible to manufacture commercial chips that act as an integrated computer. There are several types of integrated circuits that act as an integrated computer, and in this research the focus is placed on 3 types of such integrated circuits: application specific integrated circuits (ASIC), field programmable gate arrays (FPGA) and microcontrollers.

ASICs are designed to accomplish specific tasks, but not suited for general purpose use. Using an ASIC for a nanosatellite requires designing the ASIC and getting it fabricated. A mistake in the design may require a new design to be created. Redesigning and fabricating a new ASIC requires extra time and money [22]. As the research is focused on designing a general purpose OBC for nanosatellites, the inflexible nature of ASICs puts them at a disadvantage; other options on the market can provide the necessary flexibility without the need to fabricate custom components.

FPGAs are components that are mass produced and are available commercially but are still very flexible as developers can program the device to perform the functions they need. FPGAs work by having developers program the logic connections in them directly to form digital circuits [8]. The main drawback of FPGAs is the necessity to program the built in logic gates to create the required digital circuits.

Radiation tolerant and radiation-hardened FPGAs are designed to be more resilient to the effects of radiation. Both types cost significantly more than an equivalent FPGA due to

the different fabrication processes required, extra testing and validation in development and a limited market demand for them. Non-radiation hardened components are as susceptible to single event effects (SEE) as any other CMOS device [23], including memory modules and microcontrollers.

Radiation hardened and radiation tolerant FPGAs are commonly used in commercial spacecraft as they provide the necessary flexibility to be customized to perform a variety tasks from communication interfaces to digital signal processing as well as protection from effects of radiation that will prolong the life of the mission and reduce the chances of errors occurring. The flexibility of FPGAs means that less variety of radiation hardened components are required as they can be programmed to perform different functions.

FPGAs have been flown on a variety of missions such as the communication satellite Optus C1 launched in 2003. The popularity of FPGAs in space means that future missions also plan to use them as part of their design such as the UKube-1 CubeSat planned to launch in 2013. Both carry FPGAs designed by the company Xilinx. UKube-1 is planned to carry radiation hardened FPGAs in order to test and validate their performance in space conditions [24]. Optus C1 is carrying radiation tolerant FPGAs to perform data processing as part of the communication system [25].

There are 3 main types of FPGAs, they are antifuse, Static random access memory (SRAM) and Flash based. Antifuse FPGAs are one time programmable devices which contain antifuses. An antifuse is a component which conducts electricity when it is burnt.

By selecting the antifuses to burn, logic gates can be connected to form a digital circuit.

There is no way to restore them to a non conductive state which is why they can be programmed only once.

SRAM based FPGAs are volatile and require constant power to maintain their configuration, they are programmed on every start up from either an external source or an internal Flash source. Flash based FPGAs are non volatile and will maintain their configuration when there is no power.

When examining the power consumption of the 3 types of FPGAs it can be seen that SRAM based FPGAs have high power demands due to their volatile nature as the entire configuration requires a constant power supply in order to maintain its state while Flash based FPGAs and antifuse FPGAs do not have such an issue and therefore have lower power consumption in general.

The third examined technology is microcontrollers. Microcontrollers are integrated circuits that contain circuits designed for specific functions. A key difference between FPGAs and microcontrollers is that with an FPGA a developer designs the circuits using the logic gates on the FPGA while with a microcontroller the circuits already exist and can be configured through programming.

Modern microcontrollers provide many capabilities such as timing circuits, communication peripherals and interfaces to common devices (external memories, clocks, etc.). Operation of microcontrollers is performed by writing to hardware registers and those in turn manipulate the circuits that they control.

Radiation hardened microcontrollers also exist such as Aeroflex's UT80C196KD, though the commercial selection of such devices appears to be more limited in comparison with radiation tolerant and hardened FPGAs. CanX-2 CubeSat from UTIAS/SFL contains an ARM7 microcontroller, model number AT91M48200A [14], which is a non radiation hardened or tolerant component. CanX-2 was launched in 2003 and is still operational as of 2012. SwissCube-1 is a CubeSat designed by Ecole Polytechnique Fédérale de Lausanne and it uses a microcontroller as part of the attitude control system. The microcontroller that SwissCube is using is the MSP430F169 made by Texas Instruments [26], which is also a non radiation hardened component.

Examining the 3 technologies, the microcontroller stands above the rest as it requires the least amount of customization. Microcontrollers are commonly used in ground based applications and have been used in space applications as well. FPGAs require the use of a complete configuration of each circuit to be used while microcontrollers have all circuits built in and are simply selected. Through the availability of common interfaces on a typical microcontroller, it can be connected to other systems through the use of its built in circuits and hardware registers.

There are many different types of microcontrollers that can be chosen and many of them are equivalent in capabilities such as the amount of peripherals present, operational temperature range, power requirements and price. The AT91SAM9G20 was chosen as The Linuxstamp I and II used its predecessors the AT91RM9200 and the AT91SAM9260 respectively. Several months after the AT91SAM9G20 was chosen to be used on the

present OBC design, a second version of the Linuxstamp II was released with the AT91SAM9G20 as its microcontroller. The OBC schematics were complete at that stage and work was focused on the layout.

#### **2.3.2.** Memory

Memory is used to store data and programs that are used by the computer. The microcontroller itself contains embedded Read Only Memory (ROM) and SRAM which are 64KiB and 32KiB in size respectively [27], and is configured to boot from external memory storage.

Memory can be classified into 2 categories: volatile and non-volatile. Volatile memory is a type of memory that requires constant power in order to maintain the information stored within it. Non-volatile memory will retain its data even when no power is supplied to it. Traditionally, volatile memories provide faster access times to the data stored within them and have a higher tolerance to wear than non-volatile memories. Exceptions may be found in emerging technologies and highly advanced and expensive products, one of which will be discussed later. The problem of such technologies is that they are expensive. An everyday example is seen when comparing solid state drives to hard drives where the solid state drives are more expensive per unit of memory. Due to the limitations and advantages of the 2 categories of memories as outlined above, it is therefore common practice to have both types of memory if space permits.

While it is possible to have only non-volatile memory on the present OBC design, all results from computations and executing processes have to be stored in a dedicated

partition of that memory, continuous operation causes wear on the memory circuitry and the slow access times are apparent when addressing large amounts of data.

The OBC therefore contains 2 main types of memory as well as a third type to be used as backup and to evaluate its performance.

# **Non-Volatile Memory**

The selection of a non-volatile memory for a nanosatellite mission depends on several criteria: size, power consumption, price and durability. In space, access to the satellite may not be available at all times of day. Data that the satellite collects and produces must be stored in a memory location so that the satellite can access it at a later time, possibly to transmit it to a ground station.

A comparison of several types of non-volatile memory technologies are listed in Table 2, the devices chosen are commercial devices that are available directly from distributors. The characteristics portrayed are typical to devices from other manufacturers. Memory size is a critical criterion for selecting the non-volatile memory. The memory is used to store both the software for the nanosatellite operation as well as any data gathered by any sensors or other subsystems that are a part of the nanosatellite. As mentioned previously, constant access to a nanosatellite may not be possible and it may be desired to store data on-board until it can be retrieved. Being a generic system, the present OBC design may be connected to a variety of sensors, each with its own memory requirement. It is also not possible to predict the size of the control software itself.

Chapter 3 outlines minimum memory requirements for the software, in the form of a kernel and filesystem, to be used on the present OBC design. The kernel and filesystem provide a basic structure upon which applications to control a nanosatellite can be executed.

**Table 2: Comparison of Non-Volatile Memories**

| Type               | Nand Flash [28]        | Nor Flash [29]         | FRAM [30]               | EEPROM                 |

|--------------------|------------------------|------------------------|-------------------------|------------------------|

| Device             | MT29F2G08ABAEAWP-IT    | MX29GL256FLT2I         | FM23MLD16-60            | M95M02-DR              |

| Manufacturer       | Micron Technology      | Macronix               | Ramtron                 | STMicroelectronics     |

| Cost               | \$7.20                 | \$5.78                 | \$72.04                 | \$6.11                 |

| Memory             | 256MiB                 | 256MiB                 | 1MiB                    | 256KiB                 |

| Durability         | 10 <sup>5</sup> cycles | 10 <sup>5</sup> cycles | 10 <sup>14</sup> cycles | 10 <sup>6</sup> cycles |

| Power <sup>1</sup> | 115mW                  | 66mW                   | 46.2mW                  | 16.5mW                 |

Power estimated from peak current estimates in datasheet and operational voltage

The high cost and low memory size of Ferroelectric random access memory (FRAM) eliminate it as a viable option for use as a main memory. As outlined in chapter 3, the Linux kernel by itself is around 1.0MiB and therefore there would be no room for any other software or data. The Electrically Erasable Programmable Read Only Memory (EEPROM), though inexpensive, contains less memory than the FRAM and therefore is also not a viable option.

Flash memory is a commonly used technology, often seen in the form of Flash Drives. Further characteristics of the 2 types of Flash technologies are listed in Table 3. It is important to note that the timing characteristics were estimated based on information in the product datasheets and can deviate from the timings presented depending on the order of operations. The NAND Flash exhibits faster timing characteristics in all operations as

well as a lower pin count. A lower pin count leads to a simpler layout which is a strategic choice when dealing with limited PCB space.

**Table 3: Comparison of Flash operations**

| Specific device                    | MT29F2G08ABAEAWP-IT<br>[28] | MX29GL256FLT2I<br>[29] |  |

|------------------------------------|-----------------------------|------------------------|--|

| Manufacturer                       | Micron Technology           | Macronix               |  |

| Pins                               | 23(8 bit)/31(16 bit)        | 51                     |  |

| Read time per byte <sup>1</sup>    | 12ns                        | 20ns                   |  |

| Write time per byte <sup>1</sup>   | 100ns                       | 5500ns                 |  |

| Erase time per byte <sup>1,2</sup> | 5.5ns                       | 570ns                  |  |

<sup>&</sup>lt;sup>1</sup>Computed using estimates from datasheet

# **Volatile Memory**

Volatile memory is needed for the OBC in order to prolong the lifetime of the system by reducing the wear on the non-volatile memory. This is achieved by allowing the microcontroller to store and retrieve temporary data from the volatile memory as opposed to the non-volatile memory. There are several types of volatile memory that can be used and they can be divided into 2 major groups: static random access memory (SRAM) and dynamic random access memory (DRAM).

The key difference between the 2 groups is that DRAM uses capacitors to store the memory state and because capacitors lose their charge over time, it must be refreshed periodically [31]. SRAM does not suffer from the same problem as the state of an individual bit is stored within a network of transistors [32] [33]. In both cases, once the power to the memory is lost, the state of the bit storage circuits is lost with it. A key

<sup>&</sup>lt;sup>2</sup>Erase operation is performed on bulk sections and cannot be performed on smaller sections

advantage of DRAM over SRAM is that it has higher memory density as well as cheaper cost per bit [34]; for the purpose of nanosatellite OBC design, therefore, DRAM is preferred to SRAM.

The most commonly used DRAM variants are the synchronous DRAM (SDRAM) type memory. SDRAM has also developed over the years and new types of SDRAM have appeared in the market known as double data rate SDRAM (DDR SDRAM, or simply DDR) and the original synchronous design has been renamed to single data rate SDRAM (SDR SDRAM, or simply SDRAM). The difference is that DDR is able to obtain double the data rate transfer by transferring the data on both the falling and rising edge of the clock while SDR uses only one of the edges.

The chosen microcontroller, AT91SAM9G20, provides a built in controller for SDRAM but it only supports the SDR SDRAM type as it does not provide pins for the additional control pins that are required for a DDR type memory [27]. The lack of support for DDR limits the system to the use of SDR SDRAM. This can be seen as a benefit to nanosatellites as the frequency of operation increases, power consumption may increase.

Several manufacturers sell SDR SDRAMs commercially but Micron Technology products dominate the market and are available for purchase at small volumes from distributors. Products from other manufacturers require minimum orders of 1,000 to 2,500 units.

There are several important criteria for choosing an SDR SDRAM (henceforth referred to as SDRAM), they are memory size, price, speed, temperature range and power

consumption. The SDRAM units manufactured by Micron Technology are similar in functionality and requirements and therefore the most cost effective solution was chosen.

The SDRAM that is used on the present OBC design is the MT48LC16M16A2 manufactured by Micron Technology. A summary of the characteristics of the chosen SDRAM are listed in Table 4.

**Table 4: Specifications of Chosen SDRAM [35]**

| Part                         | MT48LC16M16A2P-75 IT:D TR |  |

|------------------------------|---------------------------|--|

| Manufacturer                 | Micron Technology         |  |

| Voltage                      | 3.3V                      |  |

| Capacity                     | 32MiB                     |  |

| Bus Width                    | 16 bit                    |  |

| Price                        | \$8.73                    |  |

| Temperature<br>Range         | -40°C ~ 85°C              |  |

| Power (Active<br>Read/Write) | 0.45W                     |  |

| Power (Active<br>Standby)    | 0.13W                     |  |

# **Experimental Memory**

An additional 3<sup>rd</sup> type of memory was added to the OBC design for the purpose of evaluation of its performance in the space environment. The magnetoresistive random access memory (MRAM) is a non-volatile memory that works by changing the state of a bit cell structure through a magnetic field. The magnetic field causes the bit cell to become a high resistance structure or a low resistance structure which maintains its state once the magnetic field is removed [36], several technologies exist that accomplish that goal.

The often cited advantages of MRAM are its high speed, non-volatility, high data retention and unlimited endurance. Development of MRAM has a focus of the technology to become an alternative to both Flash and SDRAM. In reality the technology of MRAM is not yet at a stage where it is able to compete with Flash as the memory density of MRAM is significantly lower. The Flash that was chosen for the OBC is 256MiB in size while a typical commercial MRAM is 2MiB in size. In addition, the speed of MRAM, while surpassing that of Flash, is not on par with SDRAM. Nonetheless, the companies and researchers working on MRAM technology have made progress over the years and are forecasting the possible replacement of Flash by MRAM.

The inclusion of the MRAM on the present OBC design is to utilize the nanosatellite platform as a vehicle suited for technology demonstration. An MRAM component from ÅAC Microtec has flown on a Japanese satellite in 2009. The magnetometer that the MRAM was a part of was reported to have worked as intended; however, there are no public reports of the performance in space of the MRAM component such as bit errors, speed and power consumption.

The MRAM on the present OBC design is intended as a backup memory where a copy of the bootloaders and kernel will be stored. The software within the MRAM will be compared to software in the NAND Flash. The research of MRAM performance in space conditions is promising and ground tests deemed its performance satisfactory though there is concern of possible latchups occurring [37], though this is true for other CMOS based devices which are not radiation hardened.

The commercial availability of MRAM is limited as it is not a commonly used technology. The MRAM devices used on board Sprite-Sat are manufactured by Freescale Semiconductors though they are not easily obtainable in low volumes. Everspin semiconductor is another manufacturer that has MRAM components on the market available in low quantities. A comparison between 2 parts from the 2 manufacturers is displayed in Table 5. The determining factor for selecting a component was the ready availability of the Everspin Technologies product.

**Table 5: Comparison of MRAM Products**

| Part Number           | MR4A16BCYS35          | MR2A16ATS35C-ND                |  |

|-----------------------|-----------------------|--------------------------------|--|

| Manufacturer          | Everspin Technologies | Freescale Semiconductor        |  |

| Price                 | \$40.07               | Unavailable                    |  |

| Memory Size           | 2MiB                  | 2MiB                           |  |

| Power Supply          | 3.3V                  | 3.3V                           |  |

| Operating Temperature | -40°C - 85°C          | 0°C-70°C                       |  |

| Operating Power       | 0.36W (write),        | 0.34W(write),0.181W(read)      |  |

| Consumption           | 0.198W(read)          | 0.54vv (write), 0.161vv (read) |  |

| Data Bus Width        | 16 bits               | 16 bits                        |  |

| Rated Data Lifetime   | >20 years             | >20 years                      |  |

| Package               | 54 TSOP               | 44 TSOP II                     |  |

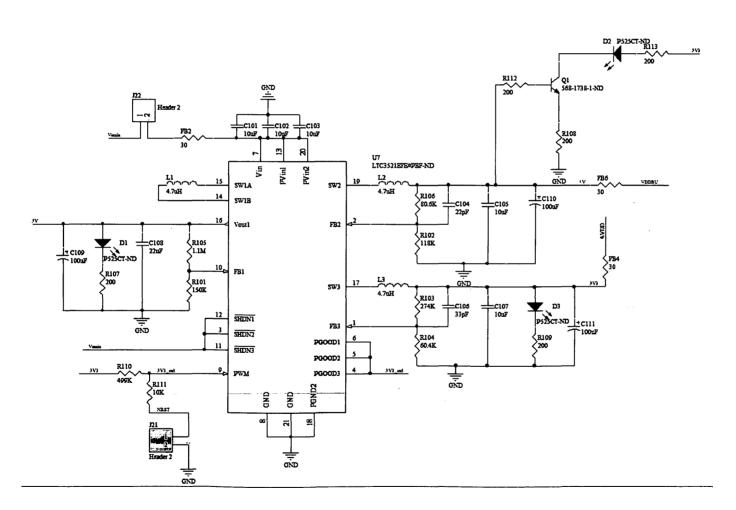

#### 2.3.3. Voltage Regulator

The main function of a voltage regulator is to maintain a steady voltage level at its output. Voltage regulators are also able to convert an input voltage level into a stable output at a different level. The OBC is composed of several active integrated circuits that require 2 voltage levels to operate; Table 6 lists the components and their operational

voltage levels. It is of note that the microcontroller requires 2 voltage levels to operate the circuitry in it.

**Table 6: Operational Voltage Levels of Active Components**

|                 | Voltage Level              |                   |

|-----------------|----------------------------|-------------------|

| Device          | Nominal (Acceptable Range) |                   |

| Microcontroller | 3.3V (3.0V - 3.6V)         | 1.0V (0.9 - 1.1V) |

| NAND Flash      | 3.3V (2.7V - 3.6V)         |                   |

| SDRAM           | 3.3V (3.0V - 3.6V)         |                   |

| MRAM            | 3.3V (3.0V - 3.6V)         | ]                 |

The inclusion of a voltage regulator as part of the present OBC design stems from making the OBC generic and independent from the power subsystem on a nanosatellite. The implementation of a voltage regulator system allows the OBC to accept a single power input at a range of values and regulate it itself. The OBC is a critical subsystem of a nanosatellite and it is therefore desired to keep its power input steady. Connection to external power supplies can result in noise on the lines and voltage spikes can cause the voltage to go out of operational bounds. A voltage regulator on the OBC will minimize the noise and provide a buffer to protect the OBC from voltage spikes.

Voltage regulators are grouped into 2 main categories: linear regulators and switching regulators (hybrids also exist). The linear regulator uses a feedback loop from the output to adjust the output voltage level to the desired voltage level [38]. The greatest disadvantage of linear regulators is their inefficiency. The input and output current of a linear regulator must be identical and as such the difference in voltage between the input and the desired output is dissipated as heat.

Switching regulators work by switching its output on and off using a circuit that is more complex than that of a linear regulator. During its on stage, the regulator transmits all the power from its input and during its off stage, it transmits no power [38]; this makes the switching regulator more efficient than a linear regulator as it does not dissipate the power difference between the input and output. The time that the device is off and on (the duty cycle) controls the output voltage at the output.

For the present OBC design, a switching regulator is preferred to a linear regulator based on its efficiency. To meet the requirement of 3.3V and 1.0V supplies, a voltage regulator with dual outputs is needed.

The LTC3521 is a switching regulator from Linear Technology and is selected because it contains 2 buck converters and 1 buck-boost converter. The buck converters are set to output 1.0V and 3.3V each with a maximum current of 600mA to meet the voltage requirements of the OBC components. The buck-boost converter is set to output 5V; this output is mostly used as a generic output that can supply power to other components. A level of 5V is selected as it is a commonly used voltage level in digital electronics.

A buck converter steps down the input voltage to a lower voltage level up to the level of the input voltage. Therefore the LTC3521 in theory requires an input of at least 3.3V in order to output a stable 3.3V and 1.0V to power the OBC. Inefficiencies due to energy loss in the form of heat in the regulator as well as imperfections of control resistors cause a deviation of the output voltage compared with the theoretical output voltage. Figure 6 and Figure 7 show the output from the regulator for the 3.3V and 1.0V output

respectively. The 1.0V output is within an error of 1.2% of the theoretical value but the 3.3V output reaches an error below 1% only after an input voltage of 3.4V. At an input voltage of 3.3V, the output is 3.186V which amount to 3.45% difference. The 1.0V output is within 1.2% of the theoretical value because the input voltage is much higher and in fact the minimum input voltage to the regulator is rated at 1.8V.

Figure 6 - Output of Voltage Regulator, 3.3V

Figure 7 - Output of Voltage Regulator, 1.0V

#### 2.3.4. Passive Components

Passive components require no input power to work and therefore cannot amplify power. Power amplification occurs in active components such as transistors where an input signal can be amplified through the use of the power input to the active component. The passive components used on the OBC include resistors, capacitors and inductors. Due to space limitations, only surface mount components are used for the present OBC design. While each component is expected to accomplish a simple task (e.g. a resistor impedes the flow of current) there are different manufacturing processes as well as materials that can be used to manufacture the components. Different components of the same type can have different properties due to the differing manufacturing processes and materials used.

#### **Resistors**

The resistors on the OBC are mostly used as part of an external circuitry that is required by the integrated circuits to function, for example, the voltage regulator requires resistors in a voltage divider configuration to set the output voltage.

The 4 main types of resistor technologies and their properties are shown in Table 7, The values are based on bulk commercial availability and does not indicate special orders directly from manufacturers.

Metal foil resistors possess characteristics, such as radiation tolerance, that make them desirable for satellite use from a performance standpoint. Radiation causes resistors formed from semiconductor material to change their resistance by doping. This is not an issue for resistors formed from thin metal, such as metal foil [39]. Their high stability and resistance to radiation effects makes them suitable for space applications according to the manufacturing companies. A disadvantage of metal foil resistors is the large price per resistor as well as their availability. Getting the resistors with the necessary resistance values per the OBC design requires getting them from manufacturers. The present OBC design requires 11 different resistance values to be used throughout the design. A single metal foil resistor costs on average \$17 from distributors and few resistance values are available. The high cost of metal foil and the requirement to purchase in bulk directly from manufacturers results in a high component price. The various types of resistor technologies are listen in Table 7.

**Table 7: Resistor Technologies**

|                                            | Resistor Type                                                                                             |                                                                                                                |                                                            |                                                                                                               |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                            | Thin Film                                                                                                 | Thick Film                                                                                                     | Metal Film                                                 | Metal Foil                                                                                                    |

| Temperature coefficient                    | 100-350 ppm/K                                                                                             | 150-800 ppm/K                                                                                                  | 350-1500<br>ppm/K                                          | 0.2 ppm/K                                                                                                     |

| Tolerance                                  | 0.01%-20%                                                                                                 | 0.1%-30%                                                                                                       | 0.1%-5%                                                    | 0.01%-0.02%                                                                                                   |

| Typical Price (200Ω)                       | \$0.6 @ 0.1%,<br>25ppm/K                                                                                  | \$0.08 @ 1%,<br>100ppm/K                                                                                       | \$1.26 @ 0.1%,<br>25ppm/K                                  | \$17.53, not for 200 Ω                                                                                        |

| Resistance ranges (commercially available) | 0 - 9.1ΜΩ                                                                                                 | 0 - 100GΩ                                                                                                      | 0.1Ω - 1ΜΩ                                                 | 100Ω, 350Ω, 1 -<br>10ΚΩ                                                                                       |

| Composition                                | Thin layer of resistive material, deposited through sputtering, resistance adjusted through trimming.[40] | Mixture of metals and ceramics deposited onto a ceramic base. Can be 3 to 10 times thicker than thin film.[40] | Thin metal film<br>applied onto a<br>ceramic<br>substrate. | Metal cold rolled foil is cemented onto a ceramic substrate and photoetched to a desired resistive value.[40] |

Metal Film resistors are thicker than the metal foil resistors and tend to have higher temperature coefficient and they are often used as temperature sensing devices. Thick films, while significantly cheaper than the other types, have poor tolerances as well as large temperature coefficients while thin film resistors posses desirable characteristics. Research on specific types of thin film resistors showed that the radiation effects on the value of their resistance is deviated from their initial values by at most 2% [41].