# DEVELOPMENT OF A NANOSATELLITE SOFTWARE DEFINED RADIO COMMUNICATIONS SYSTEM

NATASHA GADKARI

# A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

GRADUATE PROGRAM IN EARTH AND SPACE SCIENCE YORK UNIVERSITY TORONTO, ONTARIO

May 2015

© Natasha Gadkari,2015

### **Abstract**

Communications systems designed with application-specific integrated circuit (ASIC) technology suffer from one very significant disadvantage - the integrated circuits do not possess the ability of programmability. However, Software Defined Radio's (SDR's) integrated with Field Programmable Gate Arrays (FPGA) provide an opportunity to update the communication system on nanosatellites (which are physically difficult to access) due to their capability of performing signal processing in software. SDR signal processing is performed in software on reprogrammable elements such as FPGA's. Applying this technique to nanosatellite communications systems will optimize the operations of the hardware, and increase the flexibility of the system.

In this research a transceiver algorithm for a nanosatellite software defined radio communications is designed. The developed design is capable of modulation of data to transmit information and demodulation of data to receive information. The transceiver algorithm also works at different baud rates. The design implementation was successfully tested with FPGA-based hardware to demonstrate feasibility of the transceiver design with a hardware platform suitable for SDR implementation.

### Acknowledgements

I would like to thank all those who have supported me and encouraged my work through my years at York University. In particular I would like to thank my supervisors, Professor Regina Lee and Professor Sunil Bisnath for their continued support and motivation as I have progressed with my research.

I would like to thank the entire YU-GNSS team at York University, both past and present members, for their friendship, continued motivation, and willingness to assist me whenever I have come across problems. In particular, Thong Thai, whose knowledge of electronics and software has proved most invaluable. I would like to thank Kavita Joshi and Gowry Sinnathambi for providing very needed distractions to otherwise stressful days. I would like to give a special thanks to Surabhi Guruprasad for being an amazing team member for our research projects and providing help whenever needed.

I would like to thank COM DEV and the Natural Science and Engineering Council for their financial support.

I would like to express my gratitude and thanks to Archit Chitnis for keeping me in line and on track as I was working towards the completion of my work and the writing of my thesis. Lastly, I want to thank my parents whose patience and support during my entire life has brought me to where I am today.

# **Table of Contents**

| Abstract                                                       | 11  |

|----------------------------------------------------------------|-----|

| Acknowledgements                                               | iii |

| Table of Contents                                              | iv  |

| List of Tables                                                 | ix  |

| List of Figures                                                | X   |

| List of Acronyms                                               | xii |

| List of Symbols                                                | xiv |

| Chapter 1 Introduction                                         | 1   |

| 1.1 Nanosatellite Missions                                     | 1   |

| 1.2 Challenges of Nanosatellite Missions                       | 4   |

| 1.2.1 . Challenges of Nanosatellite Communications System      | 5   |

| 1.3 Research Motivation                                        | 6   |

| 1.3.1 Flexibility Afforded by SDR                              | 7   |

| 1.3.2 Benefits of SDR based Nanosatellite Communication System | 7   |

| 1.4 Research Objectives                                        | 8   |

| 1.5 Thesis Outline                                             | 9   |

| Chapter 2 Software Defined Radio Technology                    | 11  |

| 2.1 Software Defined Radio                                     | 11  |

| 2.1.1 Survey of the Existing SDR Technology                    | 10  |

| 2.1.2 | 2 Historical Overview of Software Defined Radio for Nanosatellites    | 17     |

|-------|-----------------------------------------------------------------------|--------|

|       | 2.1.2.1 Configurable Space Microsystem Innovations and Applications C | Center |

|       | (COSMIAC)                                                             | 18     |

| 2.2   | Hardware Design Options for Software Defined Radio                    | 19     |

| 2.2.  | 1 Comparison between Design Options                                   | 22     |

| 2.2.2 | 2 Software Defined Radio on FPGA platform                             | 25     |

| 2.3   | Digital Communications System                                         | 26     |

| 2.3.  | 1 Frequency Baseband Modulation/Demodulation                          | 30     |

| 2.3.2 | 2 Analog Communication System                                         | 31     |

| 2.3.  | 3 Non-coherent BFSK modulator:                                        | 33     |

| 2.3.4 | 4 Non-coherent BFSK demodulator: Correlator Implementation            | 34     |

| Chapt | er 3 Nanosatellite Communications and Link Budget Analysis            | 37     |

| 3.1   | Nanosatellite Communications                                          | 37     |

| 3.2   | Antenna Configuration                                                 | 39     |

| 3.3   | Communication System Configuration Aspects                            | 41     |

| 3.3.1 | Determination of Communication Protocol                               | 41     |

| 3.3.2 | 2 Frequency Band Determination                                        | 42     |

| 3.3.3 | B Data Rate Selection                                                 | 45     |

| 2 1   | Link Pudgat                                                           | 15     |

| 3.4.1 Uplink Command Budget                               | 46               |

|-----------------------------------------------------------|------------------|

| 3.4.2 Downlink Telemetry Budget                           | 49               |

| 3.5 Nanosatellite Communications Hardware Trade-off Study | 51               |

| 3.5.1 Commercial Options                                  | 51               |

| 3.5.2 Modified Commercial Options / Customized Transceiv  | rers52           |

| 3.5.3 Software Defined Radios (SDRs)                      | 54               |

| 3.6 SDR for Nanosatellite Communications System           | 54               |

| Chapter 4 Hardware Test Platform for Implementation of S  | Software Defined |

| Transceiver Algorithm                                     | 56               |

| 4.1 FPGA-Based Hardware                                   | 60               |

| 4.1.1 FPGA                                                | 60               |

| 4.1.1.1 Digital Signal Processing (DSP) capabilities      | 60               |

| 4.1.1.2 Design Implementation                             | 61               |

| 4.1.1.3 Development Purpose                               | 61               |

| 4.1.1.4 Processors on FPGA                                | 61               |

| 4.1.2 FPGA Development Board                              | 62               |

| 4.1.3 FPGA + DSP                                          | 63               |

| 4.1.4 FPGA + hard processor                               | 64               |

| 4.1.5 Universal Software Radio Peripheral (USRP)          | 64               |

| 4.1.6  | Hardware options for Nanosatellites Communication System   | 67 |

|--------|------------------------------------------------------------|----|

| 4.2    | Universal Software Radio Peripheral (USRP)                 | 68 |

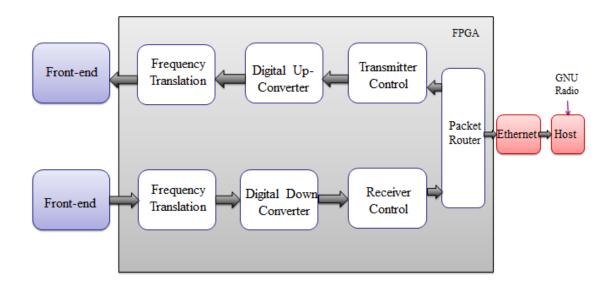

| 4.2.1  | Hardware Platform Configuration using GnuRadio             | 71 |

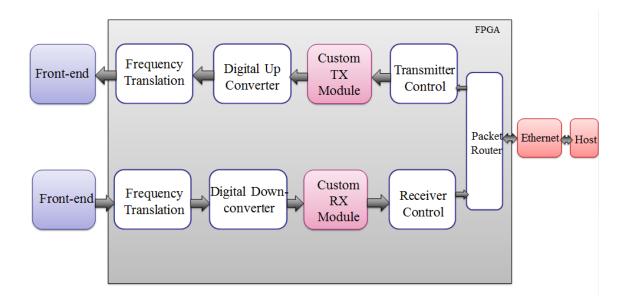

| 4.2.2  | Customization of USRP                                      | 72 |

| 4.2.3  | Software Toolbox for FPGA Implementation                   | 73 |

| Chapte | er 5 Implementation of Software Defined Transceiver Design | 74 |

| 5.1    | Γransceiver Algorithm Design Specifications                | 74 |

| 5.1.1  | Selection of Modulation/Demodulation Scheme                | 75 |

| 5.2    | Γransmitter Implementation                                 | 76 |

| 5.2.1  | Transmitter Architecture                                   | 76 |

| 5.3    | Receiver Implementation                                    | 80 |

| 5.3.1  | Receiver Architecture                                      | 80 |

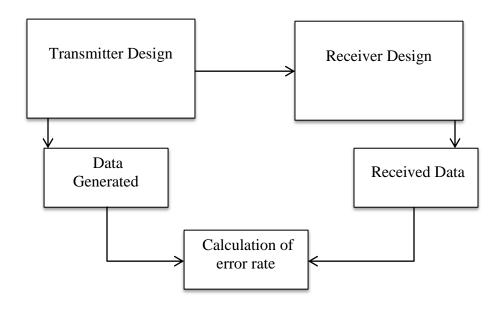

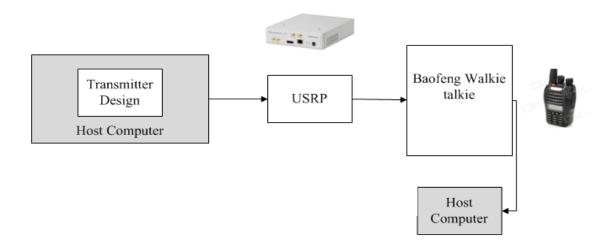

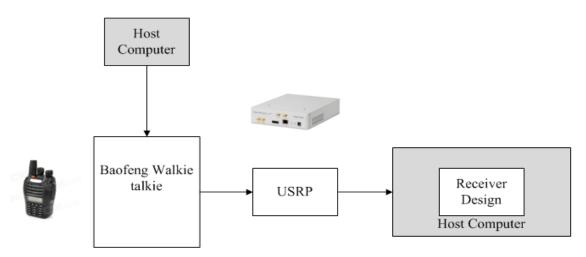

| Chapte | er 6 Transceiver Algorithm Performance Evaluation          | 86 |

| 6.1    | Test Setup                                                 | 86 |

| 6.2    | Γransceiver Design performance Evaluation                  | 90 |

| 6.2.1  | Phase 1 – Transmitter Receiver Link Simulation Results     | 90 |

| 6.2.2  | Phase 2- Tests of Transceiver Design with USRP             | 91 |

| 6.2.3  | Targeting the FPGA on USRP N210                            | 94 |

| 63 1   | Error analysis of Transceiver Design                       | 94 |

| 6.3.1 Frame Synchronization 94                                        |

|-----------------------------------------------------------------------|

| 6.4 Physical Specifications of the hardware                           |

| Chapter 7 Conclusions and Future work 97                              |

| 7.1 Summary                                                           |

| 7.1.1 Transceiver Functionality                                       |

| 7.1.2 Software Implementation of SDR for nanosatellite communications |

| system98                                                              |

| 7.1.3 Transceiver Design Hardware Implementation                      |

| 7.2 Contributions 100                                                 |

| 7.3 Future Work Recommendations                                       |

| 7.3.1 Improve Design Performance by Reducing Errors                   |

| 7.3.2 Modular standalone Software Defined Radio                       |

| 7.3.3 Protocols and Space Environment Testing                         |

| Chapter 8 References 103                                              |

# **List of Tables**

| Table 1: Physical characteristics of JPL SDR                                     | 12      |

|----------------------------------------------------------------------------------|---------|

| Table 2: Physical characteristics of Harris SDR                                  | 13      |

| Table 3: Physical characteristics of Namuru V1 and V2                            | 15      |

| Table 4: Physical characteristics of Namuru V3                                   | 15      |

| Table 5: Physical characteristics of Gemini Alpha                                | 16      |

| Table 6: Physical characteristics of GNSS software receiver for MICROSCOPE       | 17      |

| Table 7: Comparison of hardware platforms for SDR                                | 23      |

| Table 8 : Antenna designs                                                        | 40      |

| Table 9:Structure of information frame                                           | 41      |

| Table 10: Frequency bands                                                        | 43      |

| Table 11: Uplink command budget                                                  | 49      |

| Table 12: Downlink command budget                                                | 51      |

| Table 13: Comparison of FPGA hardware platforms for SDR                          | 59      |

| Table 14: Comparision between different development plaforms for SDR development | nent 67 |

| Table 15: Phase 1 test cases with results                                        | 91      |

| Table 16: Phase 2 test cases with results.                                       | 93      |

| Table 17: Physical specifications of USRP N210                                   | 96      |

# **List of Figures**

| Figure 1 : AAUSAT 3 CubeSat                                     | 3  |

|-----------------------------------------------------------------|----|

| Figure 2 : Proposed SIGMA CubeSat                               | 4  |

| Figure 3 : ISIS Full Duplex Transceiver                         | 6  |

| Figure 26: Lyrtech SFF SDR                                      | 57 |

| Figure 27: KUAR Radio                                           | 58 |

| Figure 28: PCB built around a Xilinx XC2VP70 Virtex-II Pro FPGA | 58 |

| Figure 29: Platform from NICT                                   | 59 |

| Figure 30: Atlys Spartan-6 FPGA Development Kit                 | 63 |

| Figure 31: Spartan-3A DSP 3400A Edition                         | 64 |

| Figure 32: USRP B210                                            | 65 |

| Figure 33: USRP X300                                            | 65 |

| Figure 34: USRP N210                                            | 66 |

| Figure 35: USRP E100                                            | 66 |

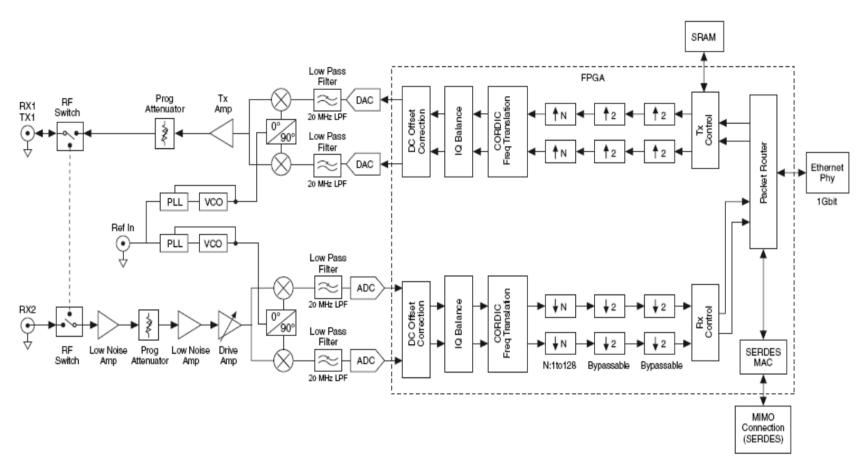

| Figure 36: Architecture of USRP N210                            | 69 |

| Figure 37: Modules of USRP N210                                 | 71 |

| Figure 38: Customization of USRPN210                            | 72 |

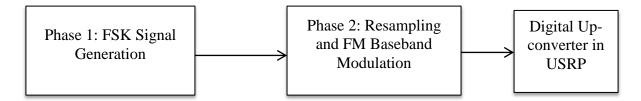

| Figure 39: Transmitter Algorithm Architecture                   | 76 |

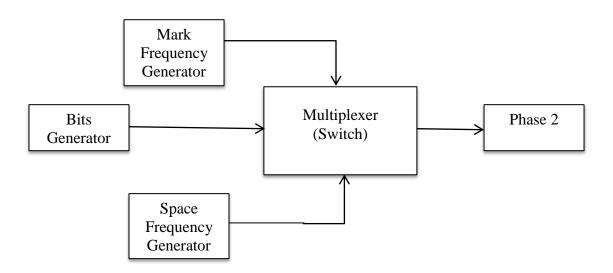

| Figure 40: Transmitter Algorithm Phase 1 FSK Signal Generation  | 77 |

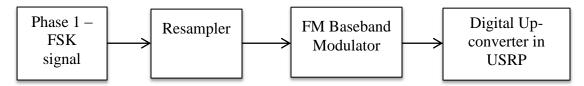

| Figure 41: Transmitter Algorithm Phase 2 Signal Transmission    | 78 |

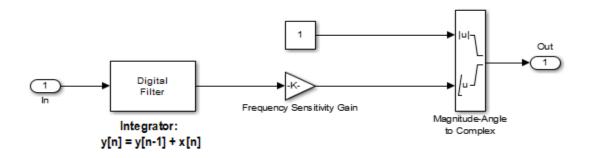

| Figure 42: Transmitter Module – Frequency Baseband Modulator    | 79 |

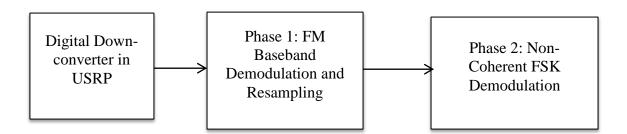

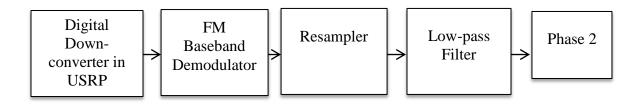

| Figure 43: Receiver Algorithm Architecture                                 | 80 |

|----------------------------------------------------------------------------|----|

| Figure 44: Phase 1 -Receiver Architecture                                  | 81 |

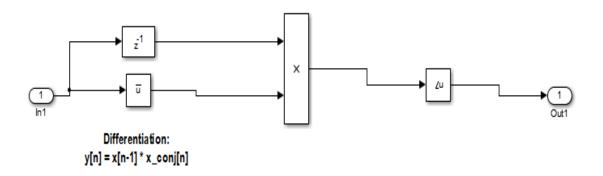

| Figure 45: Frequency Baseband Demodulator                                  | 81 |

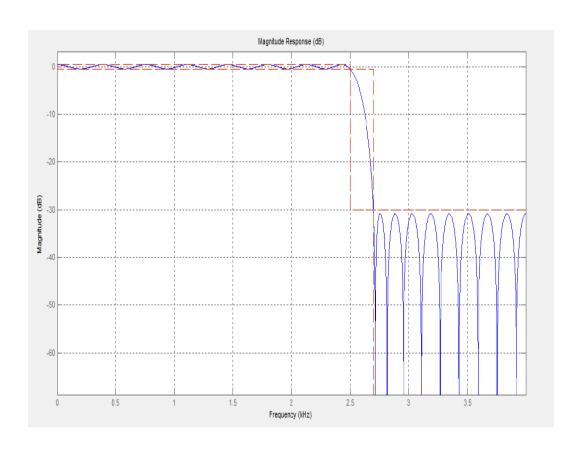

| Figure 46: Filter response of Low-pass filter                              | 83 |

| Figure 47: Phase 2- Receiver Architecture – Non-coherent FSK Demodulation  | 85 |

| Figure 48: Test Phase 1 – Communication link in Simulink                   | 87 |

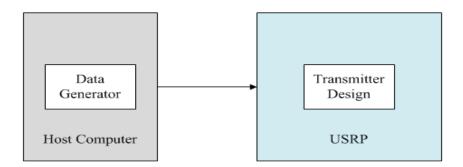

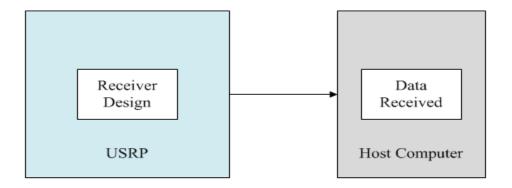

| Figure 49: Test Phase 2 – Transmitter Setup                                | 88 |

| Figure 50: Test Phase 2 – Receiver Setup                                   | 89 |

| Figure 51: Test 3 – Transmitter on FPGA                                    | 89 |

| Figure 52: Test 3 – Receiver on FPGA                                       | 90 |

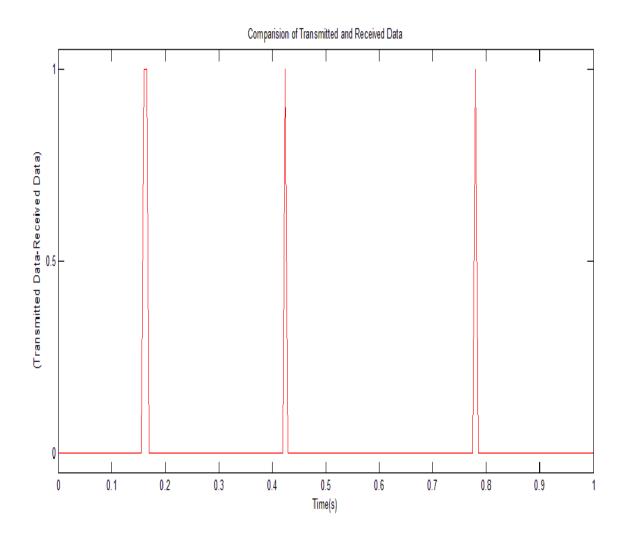

| Figure 53: Comparison of transmitted and Received Data for 1 second at 200 | 92 |

## **List of Acronyms**

ADC Analog to Digital Converter

AFSK Audio Frequency Shift Keying

ASIC Application-Specific Integrated Circuits

ASK Amplitude Shift Keying

BEE2 Berkeley Emulation Engine

BFSK Binary Frequency Shift Keying

BPS Bits Per Second

BPSK Binary Phase Shift Keying

COSMIAC Configurable Space Microsystem Innovations and Applications Centre

COTS Commercial Of The Shelf

CPM Continuous Phase Modulation

DAC Digital to Analog Converter

DPSK Differential Phase Shift Keying

DSP Digital Signal Processing

EO Earth Observation

FCS Frame Check Sequences

FFT Fast Fourier Transform

FIR Finite Impulse Response

FM Frequency Modulation

FPGA Field Programmable Gate Arrays

FSK Frequency Shift Keying

GNSS Global Navigation Satellite System

GPP General Purpose Processor

GPU Graphics Processing Unit

HDL Hardware Description Language

ISS International Space Station

KHU Kyung Hee University

KUAR Kansas U. Agile Radio

M-FSK M-ary Frequency Shift Keying

MODEM Modulation / Demodulation

OBC On-Board Computer

OQPSK Offset Quadrature Phase Shift Keying

PAM Pulse Amplitude Modulation

PID Protocol Identifier

PSK Phase Shift Keying

QAM Quadrature Amplitude Modulation

SDR Software Defined Radio

SIGMA Scientific CubeSat with Instrument for Global Magnetic field and

Radiation

SNR Signal to Noise Ratio

TEPC Tissue Equivalent Proportional Counter

TNC Terminal Node Controller

UHF Ultra-High Frequency

USRP Universal Software Radio Peripheral

VHF Very-High Frequency

WARP Wireless Open-Access Research Platform

# **List of Symbols**

| $S_1$       | Signal generated with Mark frequency          |

|-------------|-----------------------------------------------|

| $S_2$       | Signal generated with Space frequency         |

| A           | Amplitude                                     |

| $f_1$       | Mark frequency                                |

| $f_2$       | Space frequency                               |

| $\Phi_1$    | Initial phase for signal with Mark frequency  |

| $\Phi_2$    | Initial phase for signal with Space frequency |

| T, t        | Time period                                   |

| $x_C$       | Sinusoidal carrier wave                       |

| $A_C$       | Amplitude of carrier wave                     |

| $f_C$       | Instantaneous frequency                       |

| m(t)        | Message                                       |

| $\theta(t)$ | Baseband signal                               |

| $k_f$       | Frequency sensitivity                         |

| FD          | Frequency deviation                           |

| $T_S$       | Sampling period                               |

| $S_I$       | FSK modulated signal                          |

| $f_i$       | Frequency of FSK modulated signal             |

| Θ           | Phase of signal                               |

| $l_1^2$     | Output of Mark frequency correlators          |

| $l_2^2$     | Output of Space frequency correlators         |

| r(t)        | Received signal                               |

| Su          | Signal generated for Mark frequency           |

$S_S$  Signal generated for Space frequency

$S_i$  FSK modulated signal

x(t) Complex signal

u(t) Real signal

### 1 Introduction

A Software Defined Radio (SDR) is a radio in which the signal is processed entirely on reprogrammable elements (Oliveri, 2011). An SDR integrated with a Field Programmable Gate Array (FPGA) provides an opportunity to update the communication system on nanosatellites, which traditionally are physically difficult to access. Applying this technique to nanosatellites communication system will optimize the operations of the hardware, and increase the flexibility of the system. This thesis will begin with an overview of past nanosatellite missions. Then the motivation and objectives for this research is explained. Last, a thesis outline is provided.

#### 1.1 Nanosatellite Missions

Traditionally, the majority of satellites launched in the past decade have mass greater than 1000 kg. Due to the size and weight of these satellites, the structure and the development of the nanosatellite will be more complex than the small satellites, which increase the development period and manufacturing cost (Rogers et al., 2010). Due to such long development periods and high expenses, space-tested technologies were preferred to mitigate the risk of failure. Therefore the missions with the large satellites limited the scope for research of new technologies.

In the space industry, mass of a satellite is used to distinguish them. Satellites with mass greater than 1000 kg are large satellites; medium satellites have mass from 500 to 1000 kg; mini satellites with mass from 100 to 500 kg; micro satellites have mass from 10 to

100 kg; nanosatellites with mass from 1 to 10 kg; picosatellites have mass from 0.1 - 1 kg; and femto satellites have mass < 100 g (Konecny, 2004).

In recent years, technologies have been advanced in the direction of making smaller and lighter hardware components with higher capabilities. With advances in highly reliable commercial electronics and miniaturization techniques, nanosatellites are becoming popular (Rogers et al., 2010). Their main advantages over traditional satellites are much lower budgets, their modular nature and flexible launch structures. They also have significantly faster development cycles as compared to traditional satellites. The technology provides miniature and reliable satellites conducting single purpose missions (Rogers et al., 2010). Government and private sectors are showing interest in nanosatellite technology. Nanosatellites provide a suitable platform for universities and small companies to develop new space technology and demonstrate in the space field (Rogers et al., 2010). Nanosatellites are suitable for Earth observation and near- Earth missions (Trusculescu, 2012).

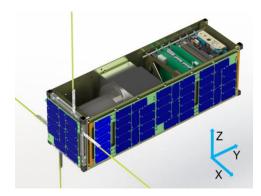

Larger satellites are still required for the outer space missions and other targeted missions that require large payloads however the new nanosatellite technology is allowing further research to be conducted for cost effective and commercial off the shelf (COTS) space tools. Figure 1 illustrates an example of a nanosatellite. AAUSAT3 (AAUSAT3, 2012) is the third CubeSat (a class of nanosatellites that conforms to CubeSat specifications published by California Polytechnic State University of 10 X 10 X 10 cm(Oliveri, 2011) built and operated by students from Aalborg University in Denmark. It was launched on 25 February 2013 from Satish Dhawan Space Centre in India on a PSLV rocket.

AAUSAT3 carries two Automatic Identification System (AIS) receivers as the main payload.

Figure 1 : AAUSAT 3 CubeSat (AAUSAT3, 2012)

Since nanosatellite missions have very constrained budgets, COTS components are used for development. Nanosatellites are used by universities to introduce the space systems engineering process to students and provide hands on training. The training includes constructing different space missions and developing hardware specializations (Rogers et al., 2010). For example Figure 2 illustrates the Sigma (Scientific CubeSat with Instrument for Global Magnetic field and Radiation) CubeSat being developed by the School of Space Research at Kyung Hee University (KHU), Korea in cooperation with the Korea Astronomy and Space Science Institute, York University and the University of New Hampshire to provide their students with training on building nanosatellite subsystems. The payloads include the Tissue Equivalent Proportional Counter (TEPC) and a magnetometer. SIGMA is a 3-unit CubeSat with a mass of 3.2 kg.

Figure 2: Proposed SIGMA CubeSat

Nanosatellites provide the opportunity to enable missions which large satellites are unable to accomplish because of their bulk nature. An example is for hardware tested on nanosatellites before being used for future missions. XI-IV developed by University of Tokyo was built for the purpose of testing a working satellite bus for future satellite missions (Klofas, 2008). Nanosatellites can provide a platform for missions which require constellations of satellites for low data rate communications that use low power for operations. Nanosatellites can present a platform for formation flying satellites so that data can be gathered for missions at several points around Earth (Yoon et al., 2014). Nanosatellites also provide the opportunity to be used for inspection of larger satellites and are also used for near-Earth space monitoring and Earth observation missions.

#### 1.2 Challenges of Nanosatellite Missions

Nanosatellite missions face a number of challenges in their development cycle. The constraint of limited mass of less than 10 kg is a major challenge as it limits the hardware that can be used for of satellite subsystems such as power, attitude control and communications. Most nanosatellites are CubeSats whose limited size of 10 cm x 10 cm

x 10 cm and mass of less than 10 kg limits the options for payload designed for research purposes. The low cost of the mission also limits the type of hardware that is feasible.

Small satellites especially nanosatellites also face the problem of limited power on a board which is small enough to fit on the satellite and capable enough to provide power to the satellite. Desktop computers and microprocessors cannot fit on small satellites, hence the computing and control of the satellite is a challenge. There is a need to use boards which will do the multiple designated functions and also fit on the satellite. The other challenges faced by nanosatellites are attitude pointing and control, propulsion and communications. This thesis is primarily focussed on the communication challenge of nanosatellites and will be discussed in the rest of the thesis.

#### 1.2.1 Challenges of Nanosatellite Communications System

The two important challenges that are faced by the communications system are structure and power. Structurally, the transceiver which consists of a transmitter and receiver needs to be reduced in size and should not be very heavy. Antennas need to be miniaturized to fit on a nanosatellite. Power is a scarce resource on a nanosatellite. Higher data rates require higher power for the communication system (Homan, 2008). Apart from structural and power constraints, the communications system needs to have a reliable link between the satellite and the ground station and the launch vehicle along with relaying the information efficiently. The communication system also requires higher data rates for effective communication at various frequency bands.

#### 1.3 Research Motivation

A successful nanosatellite mission requires an effective communication system. Historically, communication systems on nanosatellites have been built using Application-Specific Integrated Circuits (ASIC) that are designed to perform the sole function of communications. An example of a communications system built on ASIC is the ISIS Full Duplex Transceiver shown in Figure 3. The ISIS Full Duplex Transceiver (CubeSatShop.com, 2006) is designed for a CubeSat or small satellite, adds telemetry and telecommand capability and can relay data at 1200 bits per second and 9600 bits per second downlink and uses Audio Frequency Shift Keying (AFSK) for uplink. However, with the ever-growing need to use the limited space and mass on nanosatellite as effectively as possible; the motivation for this research thesis is to build a system which can aid in building more flexibility into a nanosatellite communication system in future.

Figure 3: ISIS Full Duplex Transceiver (CubeSatShop.com, 2006)

This research motivation is realistic and achievable today because of the technology advancement accomplished as part of the software defined everything technology trend (Riveria, 2013), namely Software Defined Radio systems.

#### 1.3.1 Flexibility Afforded by SDR

SDR systems rely significantly on software for their functionality, including baseband functionality, and are known to use encoders, modulators, filters and other such components of a communications system defined and designed in software (Oliveri, 2011).

The main function of an SDR is to provide increased flexibility by implementing a maximum of the communications system code on reprogrammable hardware. Different functionalities of communications system are implemented through software implementation of numerous signal processing elements. SDR's are low-cost and low-mass as there is no requirement of large and expensive hardware due to the use of software for processing (Oliveri, 2011). The radio can be reconfigured for various applications other than communications such as remote sensing, radio occultation, sensor data gathering (Davis et al., 2011) through software implementation of the functions, without having to redesign the entire hardware system.

#### 1.3.2 Benefits of SDR based Nanosatellite Communication System

An SDR-based single hardware unit can receive multiple signals over a large frequency band and process these signals in software and also allows for software-generated signals to be transmitted. These multiple functions can be implemented by changing specific software modules. Signal processing systems are developed and tested easily; and modifications and upgrades are done much more readily on the system, since it is a software module. Moreover, flexible communications protocols are developed to adapt to

the system user. Hardware radios are unable to conform to new standards or protocols, but an SDR can be reconfigured to support new standards which are developing or which may develop in the future. Other advantages of SDR's include the simplicity of quickly testing new technology, and testing individual hardware components by simulating the surrounding components in software (Oliveri, 2011).

The research presented in this thesis is an incremental contribution towards the development of a nanosatellite SDR- based communications system. Oliveri(2011) in his thesis titled "Modular FPGA Based software defined radio for CubeSats" developed a SDR hardware platform called the Configurable Space Microsystem Innovations and Applications Centre (COSMIAC) CubeSat FPGA board which can be fitted on 1U CubeSat(Oliveri,2011). The research in this thesis takes the next step to develop the software design, which does the signal processing for the communication system and presents the research objectives discussed in section 1.4.

#### 1.4 Research Objectives

The research objectives are as follows:

- To examine available technologies for nanosatellite communications system and consider SDR design as a cost-effective, flexible alternative.

- 2. To design the software implementation of SDR as a nanosatellite communications system. The proposed design is to perform signal processing for generic communication purpose. This research is an incremental contribution towards the development of a nanosatellite SDR-based communication system, as the

previous work in this field was based on COSMIAC system and tested only with GnuRadio. The proposed design eliminates the use of GnuRadio by implementing in Simulink to allow for easy porting onto the FPGA-based system

3. To implement both receiving and transmission functions of SDR. The proposed design uses software for baseband functionality in signal processing. This research implements a singular modulation scheme to demonstrate the feasibility of an SDR system for nanosatellite communications. The design is implemented on a hardware development platform which is commercial off the shelf, meets the budget constraints and can be enhanced for nanosatellites.

The research is an incremental step in the process of a developing a nanosatellite software defined radio communications system making it unique in the use of SDR for nanosatellite application.

#### 1.5 Thesis Outline

The thesis outline is as follows. The second chapter discusses the background of SDR technology. It also describes the various design options and which design option is suitable for the research objectives to be achieved. The third chapter discusses the nanosatellite communications and link budget analysis. The fourth chapter discusses the hardware platform options. It also talks about which option is chosen and the reasons for picking this option. It describes in detail the hardware platform. The fifth chapter discusses the communications algorithm implemented on the hardware. The sixth chapter discusses the experimental tests and evaluates the performance of the system. The

seventh chapter discusses the conclusions from the research and the contributions provided by this thesis. It also discusses the future work required to make this research efficient and ready to be implemented on a nanosatellite.

### 2 Software Defined Radio Technology

In this chapter, a background on SDR is provided. A literature survey of existing technology is presented as well. In addition, a number of design options are explored. And a brief background on digital communications is provided.

#### 2.1 Software Defined Radio

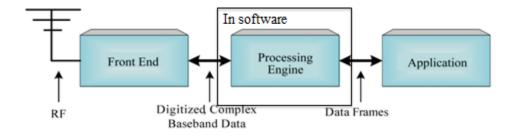

An SDR is a radio in which the signal is processed entirely on reprogrammable elements. The basic architecture of SDR is shown in Figure 4 attached with the front end and antenna. In this system, all the baseband processing of signals is done in software. As seen in the architecture, the signal is received through the antenna and then converted to the digital form in the front end. These digitized complex baseband data are then processed in the processing engine to extract data frames, which are further sent for processing for the specific application. This process can be implemented for the transmitter as well in reverse order (Oliveri, 2011).

Figure 4: SDR architecture (Oliveri, 2011)

#### 2.1.1 Survey of the Existing SDR Technology

A survey of the existing SDR Technology is presented in this section.

**JPL SDR:** The SDR has been developed for the Connect project on board the International Space Station (ISS) (Johnson, 2012). This Radio uses S- Band for communication purposes; however, it has the ability to receive L-Band signals as well. The SDR was developed by NASA and JPL.

Table 1 below lists the physical characteristic of the JPL SDR.

| Physical Characteristics |                                         |

|--------------------------|-----------------------------------------|

| Mass                     | 6.6 Kg                                  |

| Power                    | 15 W Rx(Typical) + 2W (GPS) + 65 W Tx S |

|                          | Band                                    |

| Frequencies              | S-band, L1 ,L2 and L5                   |

| Digital Processing       | 66 MHz SPARC V8                         |

|                          | 128 Mbyte SDRAM + 512 MByte Flash       |

|                          | 2x Xilinx Virtex II 3Mgate FPGAs        |

|                          | SDRAM and Flash on each FPGA            |

Table 1: Physical Characteristics of JPL SDR (Johnson, 2012)

Figure 5: JPL SDR (Johnson, 2012)

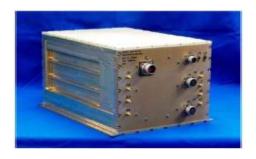

**Harris SDR:** The Harris SDR has been developed by Harris Engineering Corporation in collaboration with NASA for communication purposes on board the International Space Station (ISS). The Harris SDR is a part of the Connect project and utilizes the Ka-band for communication (Johnson, 2012).

Table 2 lists the Physical characteristic of the Harris SDR,

| Physical Characteristics |                                         |

|--------------------------|-----------------------------------------|

| Mass                     | 19.2 Kg                                 |

| Power                    | 100 W                                   |

| Frequencies              | Ka-band                                 |

| Digital Processing       | 700 MIP Power PC processor and 4 Xilinx |

|                          | Virtex IV FPGAs                         |

Table 2: Physical Characteristics of Harris SDR (Johnson, 2012)

Figure 6: Harris SDR (Johnson, 2012)

**Namuru Software Receiver Platform:** The Namuru Software Receiver platform is being developed by the University of New South Wales in Sydney, Australia (Grillenberger, 2008). There have been three versions of the receiver which have been developed so far. Namuru V1, Namuru V2 and Namuru V3. They are being developed for research purposes and have not been flown in any mission so far.

Table 3 lists the Physical characteristic of Namuru V1 and Namuru V2. Table 4 lists the Physical characteristic of Namuru V3.

| Physical Characteristics |                                       |

|--------------------------|---------------------------------------|

| Mass                     | 105 grams                             |

| Power                    | 7-9 V                                 |

| Channels                 | 12 channels                           |

| Frequencies              | L1 RF front ends, L2 up converter     |

| Digital Processing       | NiosII soft-core CPU, FPGA Altera     |

|                          | Cyclone II EP2C50F484C8, EPCS64 64-   |

|                          | Mbit flash serial                     |

|                          | Zarlink GP2015 RF chip for GPS L1     |

|                          | upconverter circuit used to configure |

|                          | second front end to GPS L2.           |

| 1 USB 2.0 and 2 RS232 interfaces,  |

|------------------------------------|

| 64 MB SDRAM and 8 MB flash memory. |

Table 3: Physical Characteristics of Namuru V1 and V2 (Grillenberger, 2008)

| Physical Characteristics |                                        |

|--------------------------|----------------------------------------|

| Mass                     | 105 grams                              |

| Power                    | 7-9 V                                  |

| Channels                 | 12 channels                            |

| Frequencies              | L1 C/A                                 |

| Digital Processing       | Zarlink GP2015 RF FE,                  |

|                          | Actel ProASIC FPGA, Actel Smart Fusion |

|                          | A2F500                                 |

|                          | upconverter circuit used to configure  |

|                          | second front end to GPS L2.            |

|                          | 1 USB 2.0 and 2 RS232 interfaces,      |

|                          | 64MB SDRAM and 8MB flash memory.       |

Table 4: Physical Characteristics of Namuru V3 (Grillenberger, 2008)

Figure 7: NamuruV1 receiver (Grillenberger, 2008)

**Gemini Alpha**: This SDR is being developed by the Microsatellites and Space Microsystems Lab of University of Bologna for the ALMASat Earth Observation (EO) mission. The applications of this SDR are for orbit determination and images georeferencing for both GPS and Galileo constellations (Avanzi and Tortora, 2010). Table 5 lists the Physical characteristic of Gemini Alpha.

| Physical Characteristics |                                            |

|--------------------------|--------------------------------------------|

| Mass                     |                                            |

| Power                    | 5 W                                        |

| Channels                 | 12 channels                                |

| Frequencies              | Dual Frequency L1/E5 or E1/L2              |

| Digital Processing       | Xilinx Virtex5 FPGA FXT series with a      |

|                          | 32-bit PowerPC PPC440 in form of hard      |

|                          | processor. External soft FPU can be        |

|                          | attached. 64 MB of 200 MHz DDR2            |

|                          | SDRAM, 16 MB of Flash memory, front-       |

|                          | ends are based on the Maxim MAX2769 IC     |

|                          | Front-end for GPS L1 or Galileo E1 signal, |

|                          | while the second is designed for           |

|                          | the L2 signal trough up-conversion from    |

|                          | 1227.6 MHz to 1575.42 MHz.                 |

Table 5: Physical Characteristics of Gemini Alpha (Avanzi and Tortora, 2010)

**GNSS Software Receiver for MICROSCOPE**: This SDR is being developed by Syrlinks of Bruz, France, to be tested on board the scientific satellite MICROSCOPE. It will be utilized for navigation and tracking applications (Grondin et al., 2010). Table 6 lists the Physical characteristic of GNSS Software Receiver for MICROSCOPE.

| Physical Characteristics |                                           |

|--------------------------|-------------------------------------------|

|                          |                                           |

| Mass                     | 0.9 kg                                    |

| Power                    | 8 W                                       |

| Frequencies              | L1/E1                                     |

| Channels                 | 9                                         |

| Digital Processing       | The signal processing functions are split |

|                          | into two main components: an FPGA and     |

|                          | a DSP                                     |

Table 6: Physical Characteristics of GNSS Software Receiver for MICROSCOPE (Grondin et al., 2010).

#### 2.1.2 Historical Overview of Software Defined Radio for Nanosatellites

Some of SDR's developed are also presented here. These were developed specifically for CubeSat missions, but do not use open source hardware and software and therefore cannot be enhanced for added applications like remote sensing, etc.

CubeSat Software Defined radio by Vulcan Wireless is a UHF transceiver designed for communications with the following specifications: direct to war fighter Communications; <sup>1</sup>/<sub>4</sub> CubeSat form factor; half duplex/full duplex configurations; and on orbit flight

heritage (Vulcan Wireless, 2010). Vulcan Wireless also offers Micro Blackbox Transponder which works with fewer protocols and supports S-Band frequencies (Vulcan Wireless, 2010).

# 2.1.2.1 Configurable Space Microsystem Innovations and Applications Center (COSMIAC)

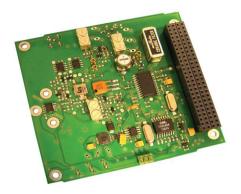

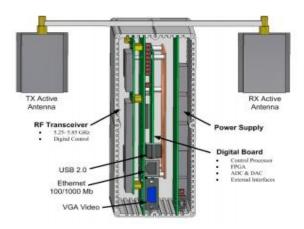

An SDR for nanosatellites is being developed by Configurable Space Microsystem Innovations and Applications Center (COSMIAC) CubeSat SDR system. COSMIAC operates at University of New Mexico in Albuquerque, NM. The SDR is developed for 1U CubeSat. It is based on the Universal Software Radio Peripheral (USRP) hardware as seen in Figure 8. The system uses the Space Plug and play Avionics (SPA) communication protocol (Oliveri, 2011). The SDR uses open source hardware and software. This system is still under development and will be flown on missions in future. This radio is of interest in this research as it shares the same hardware platform.

Figure 8: COSMIAC SDR board (Oliveri, 2011)

#### 2.2 Hardware Design Options for Software Defined Radio

SDRs are implemented on a number of hardware platforms, general purpose microprocessors (GPP), digital signal processors (DSP), graphics processing units (GPU), and field programmable gate arrays (FPGAs). In this section a short description of each of these platforms is given and their applicability for SDR.

• General purpose Microprocessors (GPP): These are processors which are found in computers. Intel and AMD devices are common Microprocessors. These devices are optimized to handle the widest possible range of applications. GPP are designed for general purpose applications and therefore are flexible. GPP's processors are designed for speed and multi-purpose usefulness (Oliveri, 2011). An SDR system containing a GPP has fixed hardware computing services and peripheral interfaces. High-level languages are implemented for operations which process incoming and outgoing data (Guo et al., 2012).

Figure 9: AMD General Purpose Microprocessor (X86 CPUS' GUIDE,2010)

Graphics processing units (GPU): These processors are designed especially for parallel architecture so that they can run vector manipulations and graphical operations. These units are excellent to create images in a frame buffer for display. The parallel structures are efficient for signal processing. The power consumption for GPU is higher than the other platforms for SDR. GPUs are manufactured by AMD and nVIDIA. SDR applications use the multi-core acceleration provided by GPUs along with the abundant parallelism functionality. The application of SDR to GPU's come with many difficulties including architectural complexity, new programming languages and different style of parallelism (Plishker et al., 2011). SDR's use GPUs for high-speed floating-point parallel arithmetic operations (Ahn et al, 2011).

Figure 10: nVIDIA GPU(TECHPOWERUP, 2015)

• Field programmable gate arrays (FPGA): FPGAs are chips that can be configured by the user after manufacture. FPGAs comprise of programmable logic components called "logic blocks" (Oliveri, 2011). FPGAs are configured using

hardware description language like VHDL, verilog. Companies that manufacture FPGA's are Xilinx and Altera.

Figure 11: Xilinx FPGA (AL Electronics, 2011)

Digital Signal processors (DSP): These processors are designed for specialized operations. They are efficient for mathematical operations and we optimized for narrower set of applications than compared to general purpose microprocessors.

Their architecture is specially designed to support the operational needs of digital signal processing. DSPs provide coding flexibility for signal processing functions and a development environment but the arithmetic operation capability does not completely support all the real-time communications operation (Ahn et al., 2011).

Figure 12: Texas Instruments DSP (AL Electronics, 2011)

FPGA + DSP: FPGAs are important for SDR applications owing to their flexibility and real-time processing capabilities. Increasing number of DSP operations are being implemented on FPGAs including operations such as digital down and up converter, FFT correlators, pulse compressions (for radar processing). FPGAs are suitable for high-speed parallel operation. However, all DSP capabilities cannot be easily implemented on FPGAs. Floating point operations are difficult to implement on FPGAs due to the large amount of memory space needed in the device. DSP and GPP platforms are better for matrix inversion (Rudra, 2004). Therefore a platform with FPGA and DSP or GPP provides a flexible platform for SDR applications.

#### 2.2.1 Comparison between Design Options

Several features of microelectronic platforms are examined to determine a feasible hardware solution for the implementation of SDR with a focus on nanosatellite communications. Table 7 compares the different hardware platforms for SDR.

|             | GPP       | DSP        | GPU       | FPGA                | FPGA+     |

|-------------|-----------|------------|-----------|---------------------|-----------|

|             |           |            |           |                     | DSP       |

| Mass        | 94g (ISIS | Varied     | 930g      | 0.19 kg             | 0.20kg    |

|             | on-board  | depending  | (Nvidia   |                     | (Spartan- |

|             | computer) | on type of | GTX 480)  |                     | 3A DSP    |

|             |           | DSP        |           |                     | FPGA)     |

| Digital-    | N/A       | Efficient  | Efficient | Reprogrammable      | Efficient |

| Signal      |           |            |           | for specialized     |           |

| Processing  |           |            |           | operations          |           |

| Operations  |           |            |           |                     |           |

| Operations  | Efficient | Not very   | Not very  | Moderate            | Moderate  |

|             |           | efficient  | efficient |                     |           |

| Size        | 96 x 90 x | Small (on  | Large     | Large               | Large     |

|             | 12.4 mm   | Integrated |           |                     |           |

|             |           | circuit)   |           |                     |           |

| Power       | Moderate  | Good       | Poor      | Moderate            | Moderate  |

| Programming | C, C++,   | C,         | CUDA, C   | Verilog, VHDL       | C, C++,   |

| Language    | Java      | Assembly   |           |                     | Verliog   |

|             |           |            |           |                     | and       |

|             |           |            |           |                     | VHDL      |

| Flexibility | High      | Low        | Moderate  | High                | High      |

| Cost        | \$6042.20 | \$600      | \$500     | \$295               | \$300     |

|             |           |            | (Nvidia   |                     | (Spartan- |

|             |           |            | GTX 480)  |                     | 3A DSP    |

|             |           |            |           |                     | FPGA)     |

| Toble 7.    | ~ •       |            | T . O O   | w CDD (Oliviani 201 |           |

Table 7: Comparison of hardware platforms for SDR (Oliveri, 2011)

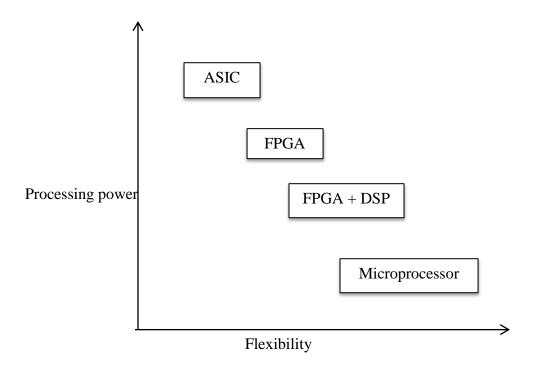

The graph below shows the comparison of the different platforms in terms of processing power and flexibility. The ideal platform for SDR is a combination of the FPGA and

DSP. DSP part of the board is efficient to perform digital signal processing tasks and the FPGA allows the flexibility of performing other operations and tasks. The power consumption of the system is also moderate.

Figure 13: Comparison of Hardware solutions based on power and flexibility (Dovis et al, 2005)

For the purpose of this research communication algorithm will be designed to implement on an FPGA only. This option is chosen so as to take advantage of the flexibility of the FPGA for DSP operations required for signal processing.

#### 2.2.2 Software Defined Radio on FPGA platform

As per the definition of SDR, the signal processing is done on a software reprogrammable element, i.e., in software. From the literature survey, it is seen that the most commonly adopted design software programmable platform is the Field Programmable Gate Array (FPGA). ASIC does have a higher processing speed and uses less power. But FPGAs have various advantages over ASIC (Application-Specific Integrated Circuit). FPGAs are reconfigurable devices which suits the main characteristic of SDR. FPGAs can be reprogrammed multiple times and allow users to define system capability as well as implement parallelization of operations. FPGAs are programmed with a hardware description language, such as Verilog or VHDL. An FPGA-based SDR use more power, but it has the advantage of flexibility and parallel operations to run simultaneously. The system is capable of parallel processing of data, multi-threaded operations and distributed computations of DSP operations. SDR applications on FPGA provide an opportunity to access and update communication system on satellites which are physically difficult to access (Oliveri, 2011). More than one digital signal processing block can be supported by the satellite with the use of an FPGA. Remote access to the firmware of the FPGA on orbit is available to upgrade or make modifications on the signal processing blocks.

There are some concepts of digital communication systems and analog communication systems which are vital to understand the design of the system discussed in Chapter 5. These concepts are discussed in section 2.3.

#### 2.3 Digital Communications System

Digital communication is the process by which digital symbols are changed into transmittable waveforms. The key aspect of a digital communications system is modulation/demodulation system (MODEM) (Wong and Lok, 2004). Modulation is the process by which the signal carrying the digital information is converted to analog waveform before being transmitted (Wong and Lok, 2004). Demodulation is the process in which the analog signal received is converted to a digital format before being processed (Wong and Lok, 2004).

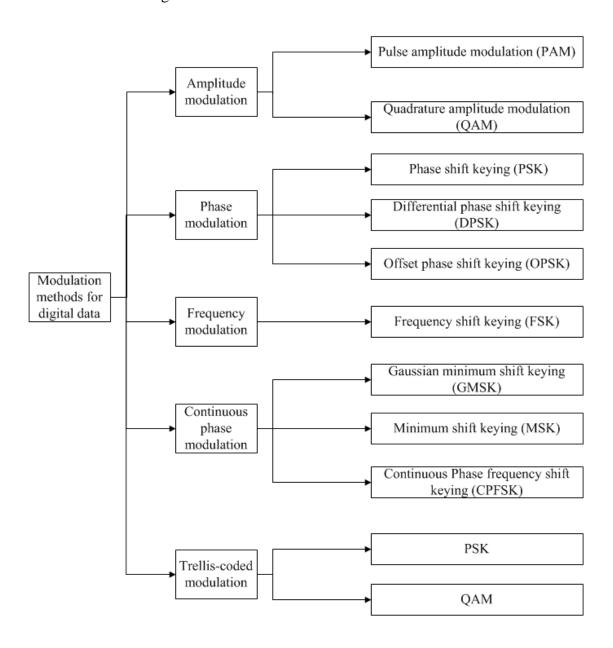

The digital modulation/demodulation techniques available are amplitude shift keying, frequency shift keying, and phase shift keying, continuous phase shift keying and the trellis-coded modulation. Figure 14 shows the different methods to modulate digital data and the variations of each of these methods.

1. ASK: Amplitude modulation of a digital data is called Amplitude Shift Keying (ASK). In this method the variation in amplitude of carrier wave is based on two or more discrete levels. In a binary message there are two levels, zero and one. The modulated binary message has bursts of sinusoid waves. The forms of ASK are Pulse Amplitude Modulation (PAM) and Quadrature Amplitude Modulation (QAM). PAM involves communication using a train of recurring pulses. The message is encoded in the form of amplitude of pulses. QAM involves the modulation of the amplitude of two waves, 90 degrees out of phase with each other (Schwartz, 1990).

- 2. PSK: Phase modulation of digital data is called Phase Shift Keying (PSK). In this method the phase of the carrier wave is varied. Binary phase shift keying (BPSK) is a form of PSK in which every phase used is assigned a particular binary number. Differential Phase Shift keying (DPSK) varies from basic PSK in that the change in the phases is the important factor here used to modulate / demodulate binary data. High state of PSK contains only one cycle whereas that of DPSK contains one and half cycle. Offset phase-shift keying, also called Offset quadrature phase-shift keying (OQPSK), uses four different values of the phase to transmit. The four values of the phase (two bits) at a time are used to construct a QPSK symbol which allows the phase of the signal to jump by about 180 degrees at a time (NI, 2007).

- 3. CPM: Continuous phase modulation (CPM) differs from coherent digital phase modulation, because the carrier phase is modulated in a continuous manner as opposed to the carrier phase resetting to zero at the start of every symbol. CPM is applied as a constant-envelope waveform (Wong and Lok, 2004).

- 4. Trellis-coded Modulation: Coding is a digital function and modulation is an analog function. Typically, most modulation schemes perform these functions separately. In trellis-coded modulation, modulation and coding are combined. The word trellis stands for the use of trellis (also called convolutional) codes (Benedetto et al., 1992).

- 5. FSK: Frequency shift keying (FSK) modulation scheme is when different frequencies are assigned to the signal (digital symbols). FSK has various

categories depending on the number of digital signals, relation between frequencies and the phase of frequencies (Wong and Lok, 2004). They are as shown in the Figure 21.

Figure 14: Modulation methods for digital data

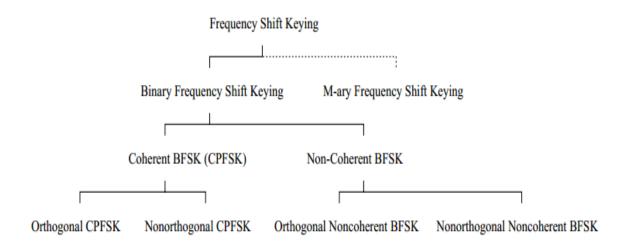

FSK is divided into two types Binary Frequency Shift Keying (BFSK) and M-ary Frequency Shift Keying (M-FSK). In M-FSK, the binary data stream is divided into n-tuples of n=log2M bits, i.e., we can send n bits or more than one bits at a time using one of the M signals that are possible. More than two frequencies can be considered in the particular modulation scheme. M-FSK is an orthogonal type of modulation.

In BFSK modulation, the frequency of a continuous carrier wave is shifted to one or two of discrete frequencies called "mark" frequency and the "space" frequency. The mark and space frequencies correspond to binary one and zero, respectively. Mark is the higher radio frequency corresponding to one. In frequency-shift keying, the signals transmitted are represented by:

Marks frequency (binary ones)

$$s_1(t) = A\cos(2\pi f_1 t + \Phi_1), 0 \le t \le T$$

(1)

where A is the amplitude,  $f_1$  and  $f_2$  are discrete frequencies,  $\Phi_1$  and  $\Phi_2$  are initial phases.

This particular system is of discontinuous phase or non-coherent, because the phase of the signal is discontinuous at the switching times and not same at any time. The signal is not continuous at bit transitions (Broendum, 1994).

BFSK can be transmitted coherently as well, which implies phase of each mark or space tone has a fixed phase relationship with respect to a reference signal phase. In this case the initial phases are the same. Non-coherent FSK is easier to generate and independent of phase changes or transitions since the two phases are different, but coherent FSK is

capable of superior error performance. In the coherent case, the phase of the transmitted signal remains continuous because the phase of the tones of each symbol is based on the previous symbol phase. Coherent and non-coherent BFSK can be divided into orthogonal and non-orthogonal. Orthogonal signalling is when the inner product of the two signals  $s_1(t)$  and  $s_2(t)$  is zero (Broendum, 1994).

Figure 15: Types of Frequency Shift Keying (Broendum, 1994)

#### 2.3.1 Frequency Baseband Modulation/Demodulation

Digital communication gives us transmittable waveforms which need to be transmitted or received. For this purpose analog transmission is required. For SDR, the theory of analog communications is used to get a complex baseband signal while transmitting and receiving a baseband signal from a complex signal.

#### 2.3.2 Analog Communication System

In analog transmissions, angle and amplitude modulation are used to transmit data or voice over wire cable, fibre or the atmosphere. By definition, angle modulation involves varying carrier wave angle by an amount proportional to the message signal. Therefore there are two types of angle modulation: frequency modulation and phase modulation (Swiggan, 1998).

Phase modulation: The phase of the carrier signal is varied to match the instantaneous phase deviation, which is the difference between the instantaneous phase and that of the carrier signal and is linearly related to the size of the modulating signal at a given time (Swiggan, 1998).

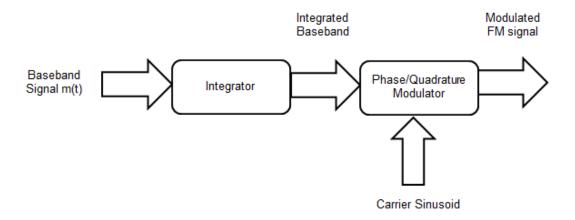

Frequency modulation: The frequency of the carrier signal is varied to match the instantaneous frequency deviation, which is the difference between the instantaneous frequency and the carrier frequency and is linearly related to the size of the modulating signal at a given time. The FM theory illustrated in Figure 22 can be explained as follows (Swiggan, 1998):

A sinusoidal carrier is represented by:

$$x_c = A_c \cos(2\pi f_c t) \tag{3}$$

where,  $f_c$  is the instantaneous frequency and  $A_c$  is the amplitude of carrier wave.

A baseband signal m(t) is modulated by first integrating the message m(t) with respect to time to get phase  $\theta(t)$ . This can be represented as:

$$\theta(t) = 2\pi f_c t + 2\pi k_f \int_0^t m(\tau) d\tau$$

(4)

$k_f$  – Frequency sensitivity, this indicates how much of the carrier spectrum the input signal should fill out. The frequency sensitivity is related to the frequency deviation by the following equation:

$$k_f = \frac{FD}{A} (2\pi * Ts) \tag{5}$$

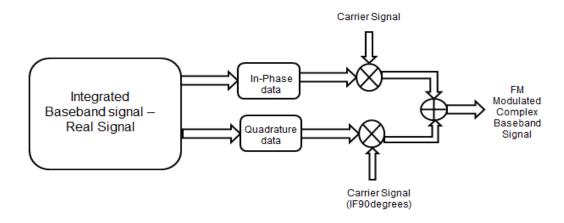

where, FD is the frequency deviation, A is amplitude of the modulating signal and Ts is the sampling period. Phase modulation is required after integrating the signal which consists of a quadrature modulator, which gives out a complex baseband signal (NI, 2014).

Figure 16: FM Modulation theory

In Figure 17 of the Quadrature Modulator, the I and Q components of the real signal are mixed with carrier signal and carrier signal with a 90 degrees phase offset to give an up-

converted signal. The up-converted signal is a complex signal in the baseband form (NI 2014).

Figure 17: Quadrature modulator

#### 2.3.3 Non-coherent BFSK modulator:

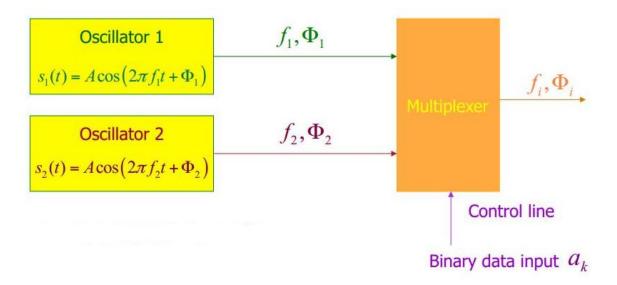

The Figure 18 shows a non-coherent FSK modulator. Conceptually, the FSK scheme involves generating the FSK signal by switching between mark  $f_1$  and space  $f_2$  frequencies. The initial phases of mark and space frequencies are  $\Phi_1$  and  $\Phi_2$  which are different from each other. Two oscillators generate the two frequency signals  $s_1$  and  $s_2$ . The binary data input controls the multiplexer. The amplitude A of the signals is same for both signals (Broendum,1994).

Figure 18: Non-Coherent BFSK Modulator

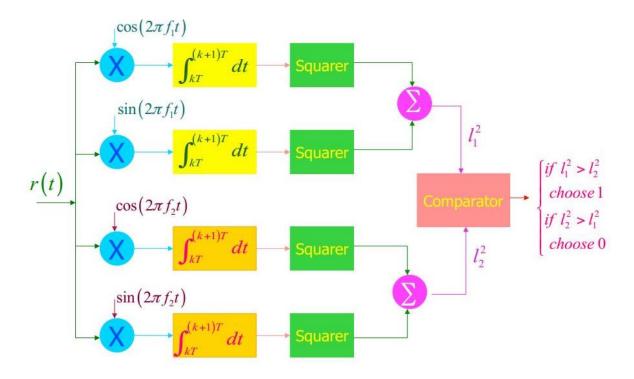

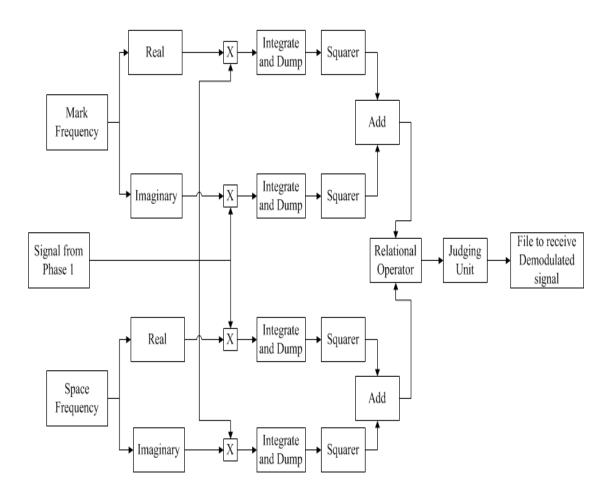

#### 2.3.4 Non-coherent BFSK demodulator: Correlator Implementation

Theoretically, in a correlator implementation as shown in Figure 19 of a non-coherent BFSK demodulator receiver, the received signal r(t) is divided into in-phase and quadrature components for each frequency component by passing it through the envelope detector. The envelope detector consists of the in-phase and quadrature correlators, integrators and the squarers. Figure 24 depicts a typical non-coherent demodulator where the upper two branches are implemented to detect  $f_1$  and the lower two to detect  $f_2$  (Broendum, 1994).

Ideally the received signal r(t) can be written as

$$s_i(t,\theta) = A\cos(2\pi f_i t + \theta), i=1,2$$

(6)

=  $A\cos\theta\cos2\pi f_i t$  (In-phase Component)-  $A\sin\theta\sin2\pi f_i t$  (Quadrature Component)

If the received signal is  $A\cos(2\pi f_1 t + \theta)$  has a phase of zero then referring to Figure 25 the first multiplication and correlation would produce an output with the highest weight and the second one would yield zero as  $\sin(2\pi f_1 t)$  is orthogonal to the signal. The third and fourth branches would also produce near-zero outputs, since their reference signals  $f_2$  are also orthogonal to the signal component (Broendum, 1994).

Similarly, if the signal  $A\cos(2\pi f_1 t + \theta)$  has an unknown phase component then, referring to Figure 25, the in-phase component the signal is partially correlated with  $\cos(2\pi f_1 t)$  and for the quadrature component the signal is partially correlated with  $\sin(2\pi f_1 t)$ . The third and fourth signals will return near-zero outputs due to orthogonality (Broendum, 1994).

After correlation and integration, the output of in-phase correlator is  $\frac{AT}{2}\cos\theta$  and  $\frac{AT}{2}\sin\theta$  for quadrature correlators. The output is squared in each branch. The outputs of the first two branches are added and then compared with the sum of the squares of the outputs from the lower two branches (Broendum, 1994).

The received signal corresponds to  $f_1$  or  $f_2$  which is evaluated by the judging unit. If we consider  $l_1^2$  as the output from the first two branches and  $l_2^2$  as the output from the last two branches then the decision is based on the following criteria (Broendum, 1994).

If  $l_1^2 > l_2^2$  then the decision is binary bit 1(mark frequency) and if  $l_2^2 > l_1^2$  the decision is 0 (space frequency). This type of receiver is called quadrature receiver. In the case of the above case where received signal is considered to be  $A\cos(2\pi f_1 t + \theta)$ ,  $l_1^2 > l_2^2$  and hence

the judging unit which compares the outputs of the two correlators will decide that binary bit 1 is the output (Broendum, 1994).

Figure 19: Non-Coherent BFSK Demodulator - Correlator Implementation

# 3 Nanosatellite Communications and Link

# **Budget Analysis**

In this chapter, a background on nanosatellite communications is provided. In addition, a survey on the antennas is performed and the process of data rate selection is also discussed. The various configuration aspects of nanosatellite communications system including the communication protocol and the frequency determination are discussed. The hardware trade-off study for nanosatellite communications system is also provided. The link budget analysis is performed and discussed as well. The benefits of using SDR for nanosatellites are also highlighted in brief in this chapter.

#### 3.1 Nanosatellite Communications

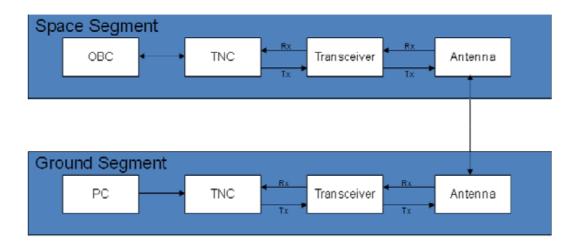

A satellite communications system can be separated in two parts as shown in Figure 20; the space segment and the ground segment. Each segment has three design components; the antenna design, transceiver development, and the communication algorithm design (Crawford et al., 2009).

The ground segment for a typical nanosatellite communications system consists of the computing station to send commands to satellites and to receive data from satellites. The station is connected to the Terminal Node Controller (TNC), which is primarily a device used for radio networks that use the AX.25 Packet protocol. It consists of a microprocessor, a modem, flash memory and software to implement the protocol and also has a command line user interface. A TNC interfaces between a computer and a radio

transceiver. The task of the transceiver is to modulate and transmit the analog radio signal containing the data. It also receives the signal and demodulates it. The transceiver is connected to an antenna which transmits and receives the data to and from the nanosatellite (Crawford et al., 2009). The space segment consists of the OBC (On Board computer) which processes data and receives and sends commands. Similar to the ground segment, the computer is connected to a TNC which in turn is connected to a radio transceiver. The transceiver is connected to the antenna (Crawford et al., 2009).

Figure 20: Communication system (Crawford et al., 2009)

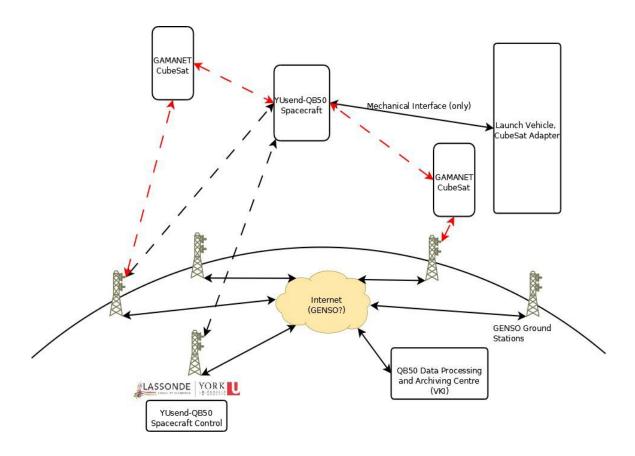

The figure below is an example of a communication network for the space segment of the satellite. As mentioned earlier, a successful satellite communication system is capable of receiving information from the ground station and transmitting information to the ground station, to other satellites and also to the launch vehicle. In satellite communications, the uplink refers to the information from the ground station to the satellite and the downlink is vice-versa.

Figure 21: Satellite Communication Network (Crawford et al., 2009)

# 3.2 Antenna Configuration

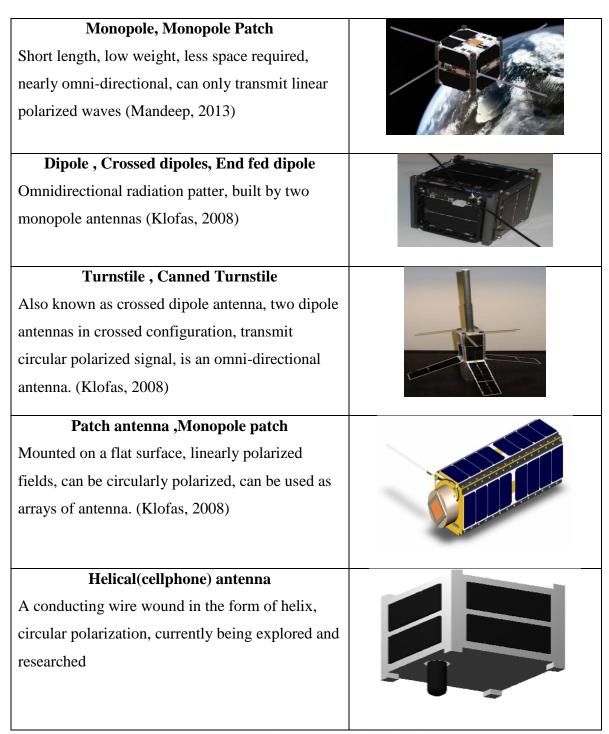

A survey of the antenna designs used on previous nanosatellite missions is presented in Table 8. The most suitable configuration is chosen based on factors such as frequency band, impedance mismatch, antenna gain, and radiation pattern. For this research a monopole antenna is used. The monopole antenna is shorter in length, has less weight and the space for mounting the monopole is less.

Table 8: Antenna Designs (Klofas, 2008)

#### 3.3 Communication System Configuration Aspects

Before describing SDR in detail, other aspects of a communications system that need to be considered and determined are discussed in this section. These include communication protocols, antenna configurations and frequency determination.

#### 3.3.1 Determination of Communication Protocol

Effective communication system entails that the satellite and the ground station must use the same communication protocol. The communication packet protocol which the nanosatellite community often uses is the AX.25 Packet protocol. The protocol is particularly designed for amateur radio operators and is used in amateur radio networks. The protocol conforms to the HDLC and ANSI X3.66 (AX.25, 1998).

The small blocks of data that are sent by the data link layer are referred to as frames. There are three types of frames: information frames carry the data that has to be communicated; supervisory frames supervise the requests for retransmission of lost or corrupted data; and unnumbered frames are used to establish and terminate link connections. Each frame has several fields. We will be focusing on the information frame in the current study. The structure of the information frame is shown in Table 9 (AX.25, 1998).

| Flag     | Address      | Control   | PID    | Info     | FCS     | Flag     |

|----------|--------------|-----------|--------|----------|---------|----------|

|          |              |           |        |          |         |          |

| 01111110 | 112/224 Bits | 8/16 Bits | 8 Bits | N*8 Bits | 16 Bits | 01111110 |

|          |              |           |        |          |         |          |

Table 9- Structure of information frame (AX.25, 1998)

A flag is used to identify the start and the end of the frames. The flag sequence is 0111111 in binary, which is 7E in hexadecimal. This sequence cannot appear anywhere else inside the frames. The address consists of the source of the frame, i.e., the source call number and the destination of the frame, i.e., the destination call number. The control field of the frame identifies the type of frame. PID Protocol Identifier (PID) is only for the information and unnumbered information frames. It identifies the type of layer 3 protocol. The information field is used to hold the data that have to be communicated and the size is 256 octets long. FCS (Frame-check sequence) is the field calculated by both the transmitting and receiving stations to insure that the frame was not altered during transmission. Bit stuffing is applied to the frames while transmitting. Bit stuffing is the process in which the transmitting station monitors the bit sequence for consecutive five bits to check whether the bits are ones. If five consecutive bits are found then a zero is inserted after the fifth bit. When the frame is received, any zero that follows five consecutive ones is discarded (AX.25, 1998). All fields are sent with the least significant bit first except for the FCS, which sends the most significant bit first.

## **3.3.2** Frequency Band Determination

Frequency bands are very important for satellite communication architecture. Different frequency bands available have different licensing requirements and applications and are listed in Table 10.

| Frequency Band            | Range               | Applications                |

|---------------------------|---------------------|-----------------------------|

| UHF(Ultra-high frequency) | 300 MHz to 3000 MHz | Extensively used for small  |

| /VHF(Very-high frequency) | 30 MHz to 300 MHz   | satellites, for links that  |

|                           |                     | requires lower data rates   |

| L-Band                    | 1 GHz to 2 GHz      | GNSS satellite systems,     |

|                           |                     | telecommunication systems,  |

|                           |                     | military                    |

| S-Band                    | 2 to 4 GHz          | Deep space applications,    |

|                           |                     | geostationary orbit, LEO-   |

|                           |                     | applications                |

| C-Band                    | 4 to 8 GHZ          | Terrestrial microwave radio |

|                           |                     | communications, weather     |

|                           |                     | radars, WIFI devices        |

| X-Band                    | 8 to 12 GHz         | Military use, coverage of   |

|                           |                     | remote areas of world,      |

|                           |                     | government and defence      |

|                           |                     | use                         |

| Ku-Band                   | 12-18 GHz           | Satellite communications,   |

|                           |                     | handle higher data rates    |

| Ka-Band                   | 23 to 27 GHz        | Future missions             |

**Table 10: Frequency Bands**

Ultra-high frequency (UHF) / Very-high frequency (VHF), the amateur radio frequency bands do not require permission from the International Telecommunications Union for use. The stations that are utilising the UHF/VHF amateur bands should have a fully licensed amateur radio operator. The UHF band ranges from 300 MHz to 3000 MHz and the VHF band ranges from 30 MHz to 300 MHz. These frequency ranges handle low data rates. UHF can be implemented using low power which requires larger antennas, a disadvantage for small satellites (Elbert, 2008).

L-Band ranges from 1 to 2 GHz. This band is particularly used for GNSS (Global Navigation Satellite System), telecommunication systems and military (Seifu 2008).

S-Band ranges between 2 to 4 GHz. Many satellites use this frequency band for transmission, especially for deep space applications and geostationary orbit missions. Signals are transmitted with low power and therefore reception requires large antennas. The difference between S-band and the amateur frequency bands is that S-band can handle higher data rates (Seifu 2008).

C-Band ranges between 4 to 8 GHz. It was the first band established for satellite communication systems. The C-Band is the frequency range in which there is also terrestrial microwave radio communications assigned. There are a number of similar systems which are located around the world, therefore a chance of interference in this range may arise (Seifu 2008). This range is also used for WI-FI devices and some weather radars (Elbert, 2008).

X-Band ranges between 8 to 12 GHz. The band is used by military due to its advantages of being resistant to rain and interference. It handles higher data rates as compared to-UHF, VHF, L- and S-bands. It can also provide coverage to remote areas of the world. This band is specifically reserved for government and defence use. A section of the X-band is allocated for deep space communications by NASA between ground stations and deep space (Seifu, 2008).

Ku-Band band ranges between 12 to 18 GHz. It is suitable for satellite communications. It uses smaller antennas and can handle higher data rates. However, the power consumption is high and the equipment required for Ku band is expensive (Seifu, 2008).

Ka-Band ranges between 23 to 27 GHz. This band will be used in future missions as it can provide more bandwidth as compared to the other bands. The primary disadvantage of this band is the attenuation caused due to rain and moisture (Seifu, 2008).

UHF/VHF is the band which requires the least power. But it is able to handle only lower data rates. The band selected at this point for the current project is UHF due to minimum restrictions on licensing requirements, power and data rate.

#### 3.3.3 Data Rate Selection

The data rate or baud rate is the definition of the speed of the data which is sent over a serial link. The unit of baud rate is bits-per-second (bps). Standard baud rates are 1200, 2400, 4800, 19200, 38400, 57600, 115200 and specifically 9600 bps as common baud rates for where speed is not important for the link (Bouwmeester, 2010). The data rates considered in this work are 200, 1200 and 1600 bps for testing and performance evaluation purposes. The 9600 bps data rate is the most common data rate used for nanosatellites in the UHF/VHF frequency range (Bouwmeester, 2010) and is therefore the targeted data rate for this work.

#### 3.4 Link Budget

The link budget is a process used to establish whether a communication link is possible by considering parameters including frequency, transmitter signal power, and bandwidth and data rate. The link budget calculates the Signal-to-Noise Ratio (SNR), which is the ration of signal power and noise power (Ps/Pn) at the receiver input (Traussnig, 2007). The link budget includes all gains and losses from baseband input to baseband

output. The link margin is a measure of the robustness of the link. As one moves to higher frequencies and one moves from fixed to mobile satellite systems the more difficult the challenge becomes and the higher the link margin must be set to provide reliable service. The link budget analysis is performed using a tool called AMSAT-IARU Link Budget calculator.

This link budget considers the desired bit rate of the system as 9600 bps and uses non coherent FSK modulation. The frequency band used is the UHF frequency band specifically the 437.475 MHz.

#### 3.4.1 Uplink Command Budget

In the uplink command budget shown in table 11, the uplink path is from the ground station to the spacecraft. The value used for the power of the ground station transmitter is a typical value used by ground stations for nanosatellite communications systems working at amateur radio frequency bands. The value is based on specifications given for QB50 a nanosatellite mission currently in the development process.

With the increasing distance between the transmitter and receiver, the power of the signal decreases (all else being equal). The received signal power will be less than the noise that is received / generated by the receiver at some point and a communication link will not be possible. The major reason for the decrease in signal power received is the loss due to the propagation distance known as the path loss or free space loss. In the uplink path from the ground station to the spacecraft the different losses considered are pointing loss, polarization loss, path loss, atmospheric losses, ionospheric losses, rain losses. At the

receiver level in the spacecraft, the antenna pointing loss, the antenna gain and the antenna transmission line losses are also taken into account. The values considered in this analysis are typical for a monopole antenna. Also at the transmitter level at the ground station, the transmission line losses and the antenna gain of the transmitter is considered. The ground station antenna considered for this analysis is a Yagi antenna. The link budget calculator provides the values for the losses pertaining to Yagi antenna.

For a desired system data rate of 9600 bps the Energy per bit to Noise Power Density Ratio which is equivalent to the "Signal-to-Noise Ratio is calculated to be 35.. The parameter is the measure of performance for the Uplink from the ground station. The system link margin is calculated to be 20.7 db from the Signal to noise ratio for the uplink. Typically for a low cost system the link margin should be around 10 db

| Parameter                                     | Value | Units |  |  |

|-----------------------------------------------|-------|-------|--|--|

| Ground Station                                |       |       |  |  |

| Ground Station Transmitter Power Output       | 40.0  | Watts |  |  |

|                                               | 16.0  | dBW   |  |  |

|                                               | 46.0  | dBm   |  |  |

| Ground Station Total Transmission Line Losses | 3.4   | dB    |  |  |